# Multi-cycle path verification method based on TCM

Qiudong Xiang, KUNLUNXIN (Beijing) Technology Co., Ltd. Wenping Guo, KUNLUNXIN (Beijing) Technology Co., Ltd. Donghui Xie, Synopsys Technology (Beijing) Co., Ltd.

# Agenda

### Introduction

- Existing SDC Verification Challenges

- Synopsys SDC Solutions

### TCM Verification

- The Flow of Formal Verification of MCP Using TCM

- The Environmental Framework for TCM verification

- The results of TCM verification

- Dynamic Verification

- VCS With SDC/SVA Simulation Flow

### Existing SDC Verification Challenges

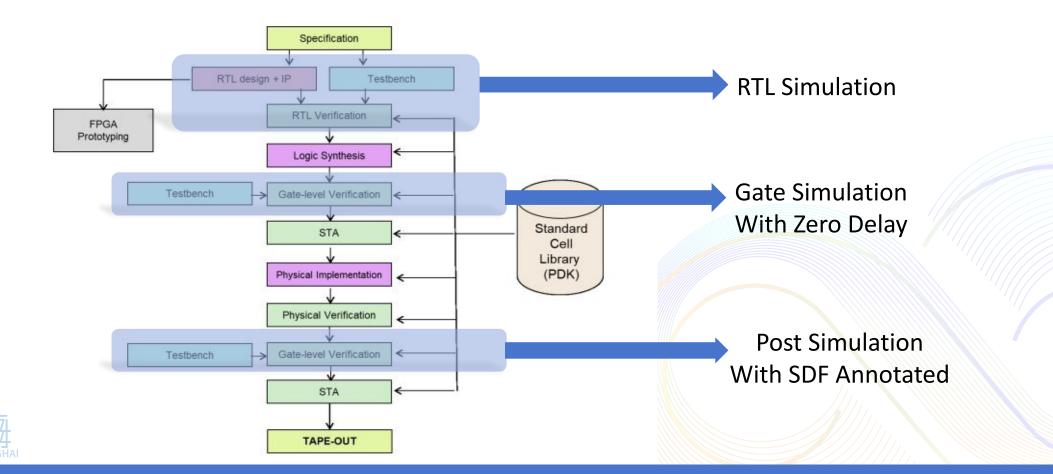

3-Stage of Verification Flow: RTL/Gate/Post-Sim

RTL-Sim focus on RTL functional issues, Only Post-Sim carry the exact timing delay information

### **Existing SDC Verification Challenges**

Performance Comparison of RTL/Gate/Post-Sim

| C       | CASE      | COMMAND  | RTL SIM | GATE SIM  | POST SIM                  |  |  |

|---------|-----------|----------|---------|-----------|---------------------------|--|--|

| S       | Same Test | simv     | 1.9h    | 23.5h     | 460h = ~19day             |  |  |

|         |           | elab     | 1.5h    | 4.2h      | 24.7h                     |  |  |

|         |           | analysis | 11min   | 90s(copy) | 113s(copy)                |  |  |

|         |           | memory   | 13G     | 306G      | 682G<br>POSTSIM/RTLSIM=52 |  |  |

| 1<br>Ac |           |          |         |           |                           |  |  |

Traditional SDC Verification covered by POST SIM, Too much TAT and Late for fixing Found MCP/FP Bugs!!!

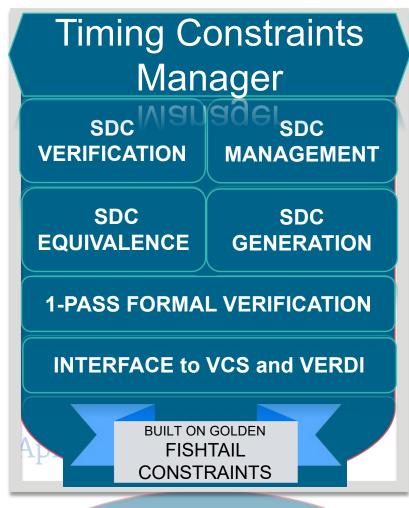

# Synopsys Timing Constraints Manager

Built on FishTail Best-in-Class SDC Constraints Solution

- Comprehensive SDC Timing Constraints Generation, Verification and Management

- Multi-Cycle/False Path Exception Verification with No Noise RTL Designers are provided precise feedback on their SDC bugs

- Comprehensive SDC Management solution

Tape-out proven promotion, demotion, mapping solution

- Automated SDC Generation from RTL Saves weeks of designer effort and development schedule

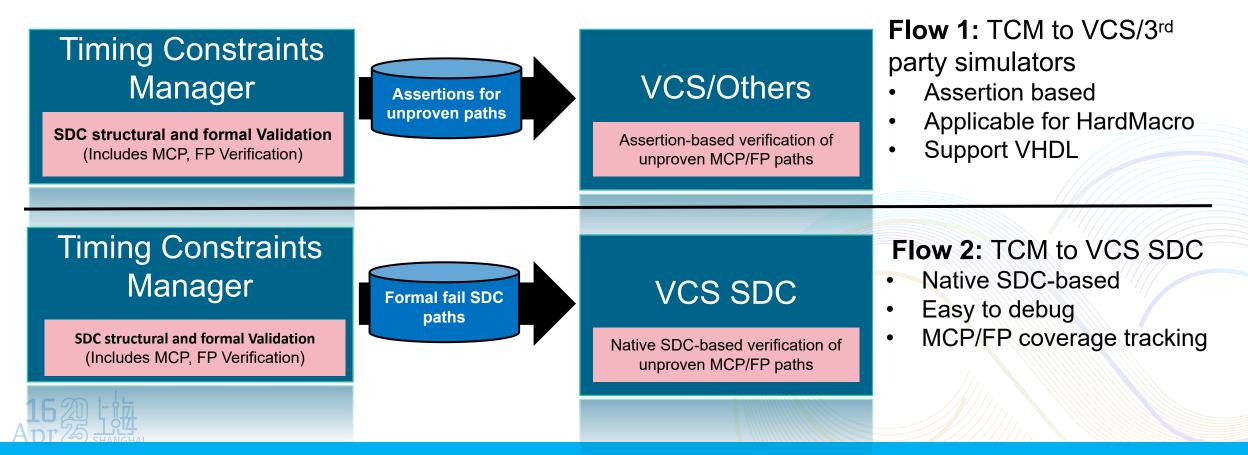

# Verify MCP/FP with Both TCM Formal engine and VCS/SDC

SDC Verification Using TCM involves multiple flows

User Can adopt either TCM SVA Flow or TCM + VCS SDC Flow based on Design Statistics

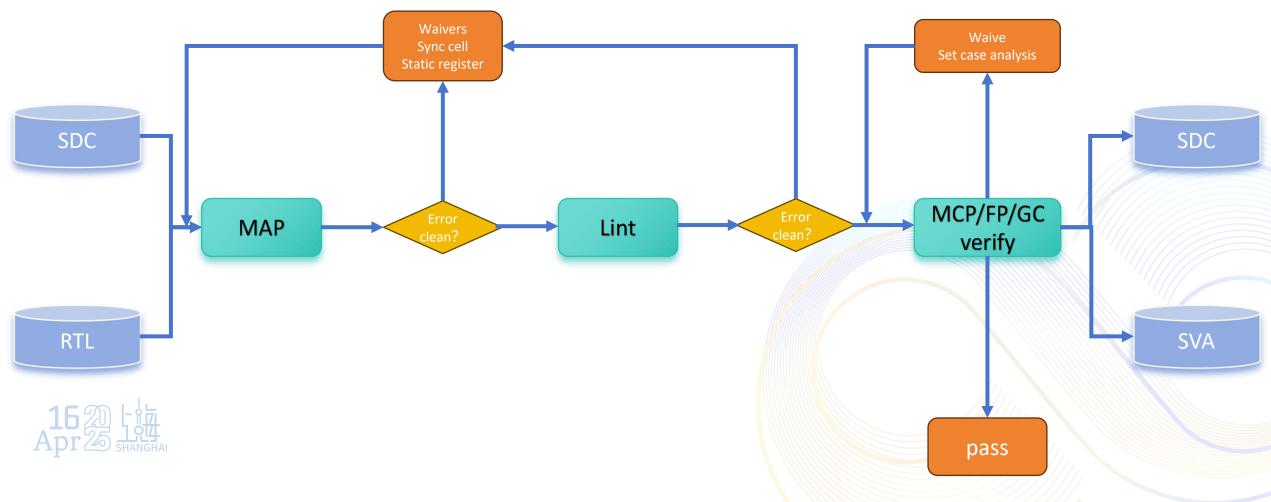

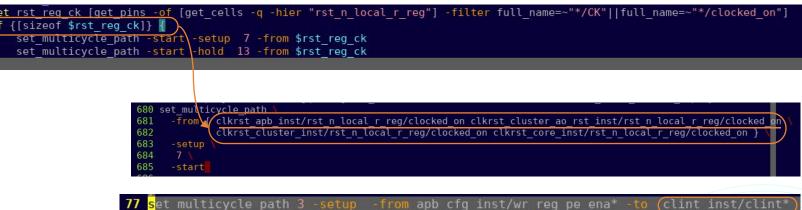

### The Flow of Formal Verification of MCP Using TCM

# TCM MAP

- Review TCM mapped SDC: •

- cd fishtail\_rtl\_verification/setup

- gvim top.syn.mapped.sdc

- Friendly for Human Reading

- Unroll the collection

- Unroll the wildcard Object

- Unroll the 'foreach'

- Support tcl-based command

et false path -from apb cfg inst/wr reg pe ena\* -to clint inst/clint\*

634 635

| foreach_in_clka [all_clocks] {                                                                                                             | 55 # From /proj/xiangqiudong/sdc_verif/top.syn.sdc li |

|--------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|

| foreach_in_clkb [remove_from_collection [all_clocks] \$clka]/{                                                                             | 56 set max delay 🔪                                    |

| set period_clka [get_attr \$clka period]                                                                                                   | 57 -from { clk core }                                 |

| set period_clkb [get_attr \$clkb period]<br>set value [expr [lindex [lsort [list \$period clka \$period clkb ]] 0] - \${MAX DELAY BUDGET}] | 58 (-to { clk_sys } \ )                               |

| if {[string match "virtual_*" [get_obj \$clka]]} {                                                                                         | 50 to ( cck_3)3 )                                     |

| <pre>set value [expr \$value + \${I0_DELAY_RATI0}**period_clka] }</pre>                                                                    |                                                       |

| if {[string match "virtual_*" [get_obj \$clkb]]} {                                                                                         |                                                       |

| <pre>set value [expr \$value + \${I0_DELAY_RATIO}**period_clkb] }</pre>                                                                    | 61 # From /proj/xiangqiudong/sdc_verif/top.syn.sdc li |

| <pre>set cmd "set_max_delay -ignore_clock_latency \$value -from \[get_clocks [get_obj \$clka]\] -to \[get_clocks [get_obj \$clkb]\]"</pre> | 62 set_false_path 🔪                                   |

| puts \$cmd                                                                                                                                 | 63 -from { clk core } \                               |

| eval \$cmd<br>set cmd "set_false_path -hold -from [get_clocks [get_obj \$clka]\] -to \[get_clocks [get_obj \$clkb]\]"                      | 64 -to { clk_sys } \                                  |

| pu <del>ts \$emd</del>                                                                                                                     | 65 -hold                                              |

| eval \$cmd                                                                                                                                 | 0.5 110 Cd                                            |

### • SDC Lint check results

- cd fishtail\_rtl\_verification/setup

- view\_fishtail\_result –Verdi

- RTL & Clock issue Flagged by TCM:

- RTL-\*

- CLK-\*

- If not fix:

- Impact further SDC Lint/Verification

- Impact Synthesis & STA QoR and Performance.

| Waive | Issues                                                            | Severity | Message Count |

|-------|-------------------------------------------------------------------|----------|---------------|

|       | Parser Issues                                                     | ]]       |               |

|       | Design Issues                                                     |          |               |

|       | Traversing a timing arc completes a combinational loop. (RTL-035) |          | 6             |

#### **Clock Definition Issues**

Setup Issues

| <pre># Virual Clock Define create_clock -name "virtual_clk_core" -  create_clock -name "virtual_clk_sys" - </pre> | Severity Message Cou                           |                        |  |  |  |  |

|-------------------------------------------------------------------------------------------------------------------|------------------------------------------------|------------------------|--|--|--|--|

| Clock is redundant. Its removal will have no impact o                                                             | n the way the design is constrained. (CLK-02   |                        |  |  |  |  |

|                                                                                                                   |                                                |                        |  |  |  |  |

| CLK-027 (1 message)                                                                                               |                                                |                        |  |  |  |  |

| Regular expression for waivers: (applies to strings inside qu                                                     | otes in message)                               |                        |  |  |  |  |

| Select all Messages Unselect all Messages                                                                         |                                                |                        |  |  |  |  |

| □Waive this message<br>Warning: Clock 'virtual_clk_core 'is redundant. Its remova                                 | l will have no impact on the way the design is | constrained. (CLK-027) |  |  |  |  |

| # Virual Clock Define                                                                                             |                                                |                        |  |  |  |  |

| <pre>create_clock -name "virtual_clk_core"</pre>                                                                  | <pre>-period \${PERIOD_CLK_CORE}</pre>         |                        |  |  |  |  |

| <pre>create_clock -name "virtual_clk_sys"</pre>                                                                   | <pre>-period \${PERIOD_CLK_SYS}</pre>          |                        |  |  |  |  |

| <pre>create_clock -name "virtual_clk_cfg"</pre>                                                                   | <pre>-period \${PERIOD_CLK_CFG}</pre>          |                        |  |  |  |  |

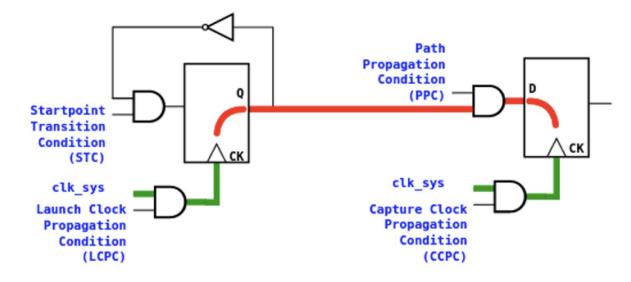

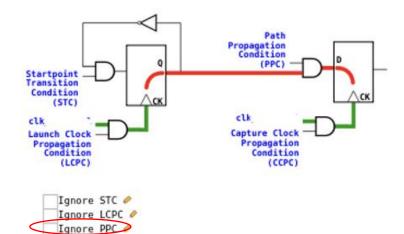

# TCM Verify MCP/FP

• TCM structurally extract for MCP/FP on Sync

### Path

- STC: Start Point Transition Condition

- LCPC: Launch Clock Propagation Condition

- PPC: Path Propagation Condition

- CCPC: Capture Clock Propagation Condition

- TCM Formal engine Verify:

- STC/LCPC/PPC/CCPC relationship

- To see any exception make Early Capture happen

🗌 The endpoint is allowed to go metastable 🤌

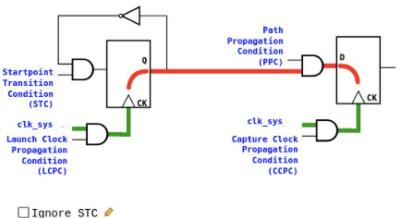

# TCM Verify MCP/FP

- MCP set on Data Path

- Known Incorrect MCP

- Formally Proven as Failed as the 'PPC' can be true

in the next clock cycle of 'STC'.

□ Ignore LCPC / □ Ignore PPC / □ Ignore CCPC /

Failure State:(=)

The path is not multi-cycle because when the startpoint transition condition is true, then in the next clock cycle it is possible for the path propagation condition to also be true. As a result, a transition on the startpoint will propagate to the endpoint in the same clock cycle.

### 78 set\_multicycle\_path 3 -setup -from apb\_cfg\_inst/wr\_reg\_pe\_ena\* -to clint\_inst/clint\*

Start/Endpoint Pairs For Clock Crossing Launch Clock clk\_sys Capture Clock clk\_sys

| <b>,1</b> 6 | Reverify | Startpoint                        | Static<br>Startpoint | Endpoint              | Waived<br>Endpoint | Waived Start<br>End Pair |   | I/O Impacted | Static | Incorrect shift |  |

|-------------|----------|-----------------------------------|----------------------|-----------------------|--------------------|--------------------------|---|--------------|--------|-----------------|--|

| Apr         | ×        | apb_cfg_inst/wr_reg_pe_ena_reg[1] |                      | clint_inst/clint0_reg |                    |                          | × |              |        |                 |  |

| <b>•</b>    | ×        | apb_cfg_inst/wr_reg_pe_ena_reg[1] |                      | clint_inst/clint1_reg |                    |                          | × |              |        |                 |  |

|             | ×        | apb_cfg_inst/wr_reg_pe_ena_reg[1] |                      | clint_inst/clint2_reg |                    |                          | × |              |        |                 |  |

# TCM Verify MCP/FP

### • Steps to review Formal Result

- 'STC/LCPC/PPC/CCPC' extracted by TCM

- Waveform Generated by TCM Formal Engine

- Check whether can apply Static/SCA?

#### Timing Path:

| Timing Arc                                                                     | <b>Propagation Condition</b> |

|--------------------------------------------------------------------------------|------------------------------|

| <pre>apb_cfg_inst/ _clk(r)-&gt;apb_cfg_inst/wr_reg_pe_ena[1]</pre>             | (1)                          |

| <pre>apb_cfg_inst/wr_reg_pe_ena[1]-&gt;apb_cfg_inst/clint_apb_wr_req</pre>     | (1)                          |

| <pre>apb_cfg_inst/clint_apb_wr_req-&gt;apb_cfg_inst/clint_apb_wr_addr[*]</pre> | (1)                          |

| apb_cfg_inst/clint_apb_wr_addr[*]->clint_inst/clint_apb_wr_addr[*]             | (1)                          |

| clint_inst/clint_apb_wr_addr[*]->clint_inst/apb_ipi_wr_sel[0]                  | v1643129                     |

| clint_inst/apb_ipi_wr_sel[0]->clint_inst/clint0_reg                            | !v1643130                    |

| clint_inst/clint0_reg->clint_inst/clk(r)                                       | (1)                          |

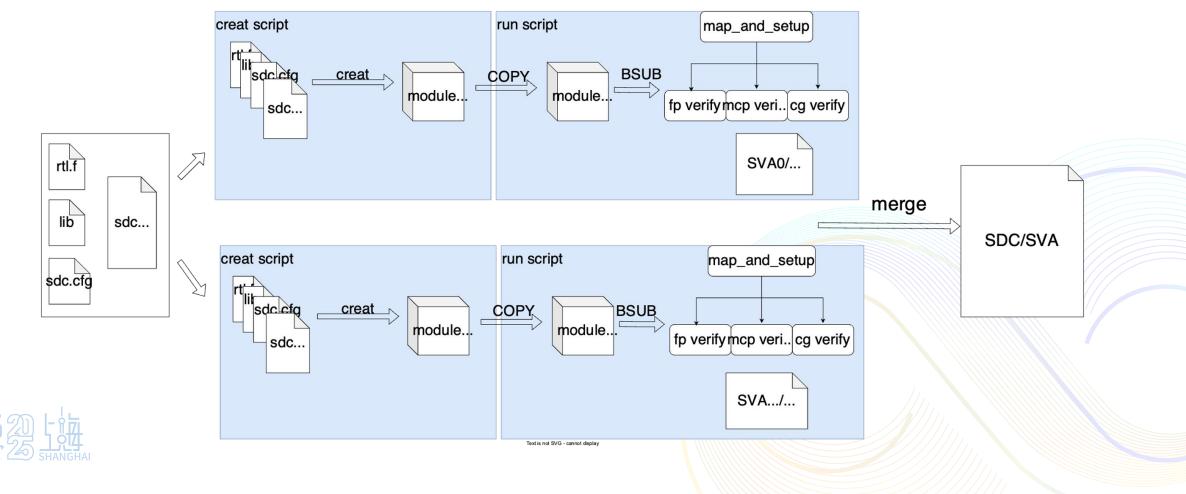

### The Environmental Framework for TCM verification

### Comparison before and after mcp splitting

| module   | sdc number | paths number | memory | run time |

|----------|------------|--------------|--------|----------|

| test_all | 10         | >100000      | >2.1T  | >15days  |

| test_0   | 2          | 11921        | 212G   | ~2days   |

| test_1   | 2          | 22354        | 455G   | ~5days   |

| test_2   | 2          | 55234        | 1T     | ~7days   |

| test_3   | 2          | 22315        | 413G   | ~5days   |

| test_4   | 2          | 11765        | 119G   | ~2days   |

### Verification Results for 24 exceptions:

#### Path Count Classification Exception Formal Pass Fail Total Runtime Count PASS 3001 15:14 7 3001 θ PARTIAL FAIL (Incorrect shift) 3 2290 2308 12:57 18 337 8839 2:16:46 PARTIAL FAIL 2 8502 NO PATHS 6 6 PASS (MCP Hold < Setup)

Total Passing Paths 13793 Total Failing Paths 355 Total Paths 14148 Passing path percentage 97%

Befor waive

#### Verification Results for 24 exceptions:

| Classification          |                    | Path<br>Count |      |      |       |         |  |

|-------------------------|--------------------|---------------|------|------|-------|---------|--|

|                         | Exception<br>Count | Formal        | Pass | Fail | Total | Runtime |  |

| PASS                    | 12                 | 28490         |      | θ    | 28490 | 21:07   |  |

| NO PATHS                | 6                  |               |      |      |       |         |  |

| PASS (MCP Hold < Setup) | 6                  |               |      |      |       |         |  |

Total Passing Paths 28490 Total Failing Paths θ 28490 Total Paths Passing path percentage 100%

Ignore CCPC 🤌

Ignore ppc

> verify the MCP paths inside the IP separately from the MCP paths at the top level of the SoC or the top level of the partitio

Empty module or set module as black box

> Skip some steps

•••••

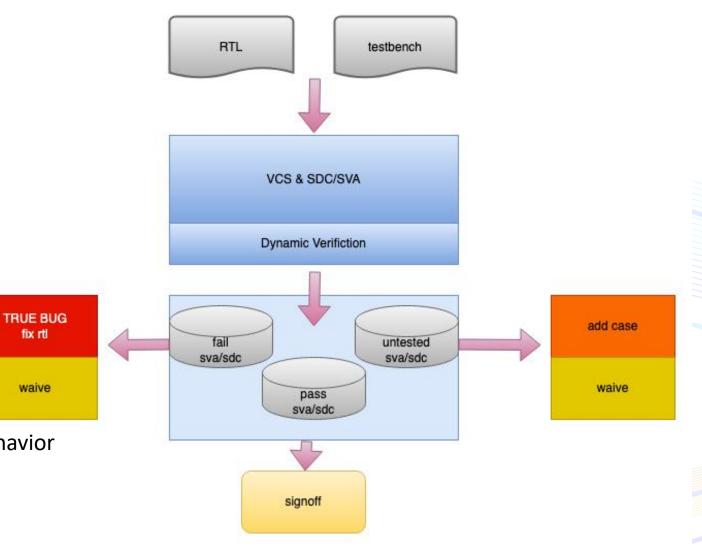

# VCS With SDC/SVA Simulation Flow

### **Solution Overview**

- Read SDC files during RTL verification

- Model timing uncertainty of waived paths in STA

- Multi-Cycle Paths, False Paths

- Two dynamic validation modes:

- X-injection

- Violation Checkers

• Advanced Features

SHANGHA

Cross-check SDC declarations with simulation behavior

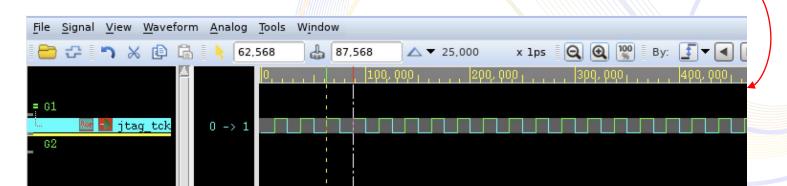

### VCS SDC RTL Simulation Result

Sanity Check for Clock & SCA

- Issues Flagged by VCS-SDC:

- set\_case\_analysis mismatch

- clock Period mismatch

130 set\_case\_analysis 0 [get\_pins "\${CORE\_TOP\_HIER}basic\_regfile\_inst/sasrl\_1p\_test1\_reg/Q"]

131 set\_case\_analysis 0 [get\_pins "\${CORE\_TOP\_HIER}basic\_regfile\_inst/sasrl\_1p\_test\_rnm\_reg/Q"]

132 set\_case\_analysis 0 [get\_pins "\${CORE\_TOP\_HIER}basic\_regfile\_inst/sasrl\_1p\_rme\_reg/Q"]

133 set\_case\_analysis 0 [get\_pins "\${CORE\_TOP\_HIER}basic\_regfile\_inst/sasul\_rm\_reg\_3\_/Q"]

134 set\_case\_analysis 0 [get\_pins "\${CORE\_TOP\_HIER}basic\_regfile\_inst/sasul\_rm\_reg\_3\_/Q"]

135 set\_case\_analysis 1 [get\_pins "\${CORE\_TOP\_HIER}basic\_regfile\_inst/sasul\_rm\_reg\_1\_/Q"]

136 set\_case\_analysis 0 [get\_pins "\${CORE\_TOP\_HIER}basic\_regfile\_inst/sasul\_rm\_reg\_1\_/Q"]

137 set\_case\_analysis 0 [get\_pins "\${CORE\_TOP\_HIER}basic\_regfile\_inst/sasul\_rm\_reg\_0\_/Q"]

SDC-ERROR: @ time 0 ps : set\_case\_analysis regfile\_inst.sasul\_rm[2], expected value 0 got 1

SDC-ERROR: @ time 0 ps : set\_case\_analysis regfile\_inst.sasul\_rm[1], expected value 1 got 0

SDC-ERROR:PERIOD @ time 62568 ps : clock dut.jtag\_tck(clk\_jtag), Observed: 25000 ps Expected: 20000 ps SDC-ERROR:PERIOD @ time 87568 ps : clock dut.jtag\_tck(clk\_jtag), Observed: 25000 ps Expected: 20000 ps

• Next Step

• Review Design/SDC/Testbench • Fix Mismatch

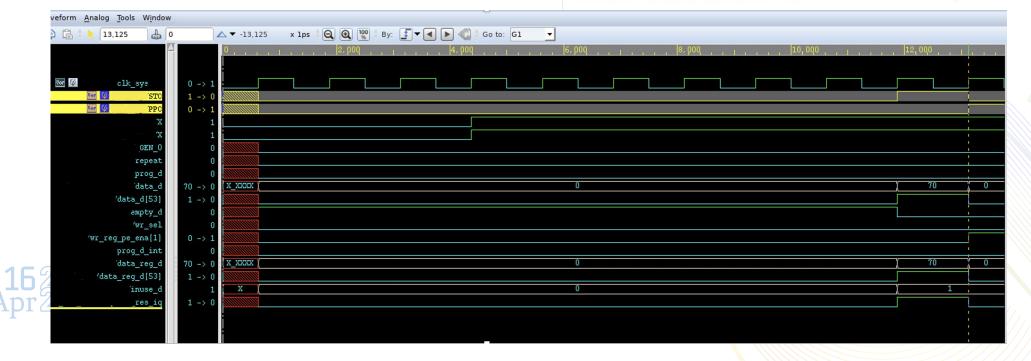

### VCS SDC RTL Simulation Result

UVM\_ERROR @ 3268832: Description: Monitor Check for X or Z on PRDATA UVM\_ERROR @ 3268832: Description: Monitor Check for X or Z on PRDATA

| = 61          |                  |                                         |

|---------------|------------------|-----------------------------------------|

|               | 🛚 🔁 clk 👘 0 -> 1 |                                         |

| 🛛 🖉 wr_reg_pe | e_ena[0] 0       |                                         |

| 📕 🔝 wr_reg_pe |                  |                                         |

|               | e_ena[2] 0       |                                         |

| <b>-</b> 62   |                  |                                         |

|               | clint0           |                                         |

|               | clint1 0         |                                         |

| Ver 🎉         | clint2 0         |                                         |

| 63            |                  |                                         |

|               |                  |                                         |

|               |                  | Ο , , , , , , , , , , , , , , , , , , , |

|               |                  |                                         |

X-Injection happens as Early Capture on MCP Path and Leads to Simulation Fatal Issue

# VCS SDC RTL Simulation Result

MCP/FP Coverage

- SDC coverage

- Total Path/violationg Path/Active Path/Inactive Path

- Next step Suggestion:

- Enhance testcase Coverage

- Review TCM Formal Verification Result

| Edit Tools Syntax Buffers Window Hel | р                                             |

|--------------------------------------|-----------------------------------------------|

| 8 8 8 % ~                            | 父 🐵 🄄 🛤 🎥 🏘 🗉 🗞 🛛 🚳                           |

| Coverage Summary                     |                                               |

|                                      |                                               |

| Total commands considered            | 973                                           |

| Violating commands :                 | 0 (0.0%)                                      |

| Active commands                      | 8 (0.82%)                                     |

| Inactive commands :                  | 745 (76.57%)                                  |

| Clock Sanity Disabled commands :     | 0 (0.0%)                                      |

| Commands with empty paths :          | 220 (22.61%)                                  |

| Total paths considered               | 35783                                         |

| Violating Paths                      | 0 (0.0%) # Paths with violations              |

| Active Paths                         | 581 (1.62%) # Active paths with no violations |

| Inactive Paths                       | 35202 (98.38%) # Inactive paths               |

| Clock Sanity Disabled Paths :        | 0 (0.0%)  # Path Disabled due to Clock Sanity |

# VCS SVA RTL Simulation Result

### SVA coverage result

|                  | NUMBER | PERCENT |

|------------------|--------|---------|

| Total Number     | 523944 | 100.00  |

| Uncovered        | 122609 | 23.40   |

| Success          | 401335 | 76.60   |

| Failure          | 290    | 0.06    |

| Incomplete       | 8      | 0.01    |

| Without Attempts | 59     | 0.01    |

# CONCLUSION

Different SDC issues caught by different Steps

|--|

- TCM

- MCP

- Missing Hold

- I/O

- Missing Delay

- Missing Drive/Load

- Clock

- Redundant Define

### Formal MCP/FP Verification

### – TCM

- Original Correct SDC

- 2 MCP on Reset Tree

- 99% Proven Pass

- 4 RTL BUGS

- MCP between Async

- SKIPPED

- Distort False MCP/FP

- 1 MCP & 1 FP

- 100% Proven Fail

### MCP/FP Dynamic Verification

- VCS SDC

- Original Correct SDC

- set\_case\_analysis issue

- Value mismatch

- create\_clock issue

- Period mismatch

- Distort False MCP/FP

- 1 MCP & 1 FP

- Fail, early capture violation

- Simulation fatal error

# CONCLUSION

### SDC Solutions Runtime Comparison

| xxx_top              | Runtime                                       | Memory        |

|----------------------|-----------------------------------------------|---------------|

| VCS (POST-SIM)       | 160h                                          | 644G          |

| VCS (RTL-Sim)        | 1h                                            | 15G           |

| TCM SDC verification | 12h                                           | 272G          |

| VCS SDC              | Elab: 13x of RTL-Sim<br>Sim: 1.04x of RTL-Sim | 3x of RTL-Sim |

# CONCLUSION

### Shift-left:

Catch SDC Bugs Earlier, Win more time for RTL modification;

Shorten TAT to effectively verify SDC/RTL modifications before RTL Frozen.

### **Comprehensive:**

TCM's Formal Engine help to catch scenarios or corner cases which is not covered by Existing testcases.

### **Smarter POST-Sim:**

Help to fine-tune Post-Sim priority

# **FUTURE WORK**

False path & group clock verification

➤ Sdc promotion flow

> More efficient result statistics for sva&vcs verification

> Explore more methods for accelerating simulation

....

# Thank You !