## Formal Verification Sign-off Methodology for Pin Multiplexing Based on Jasper CONN

Xubao.Wang (xubao.wang@unisoc.com) Chengzhe.Li (chengzhe.li@unisoc.com) Xufeng.Zhang (xufeng.zhang@unisoc.com)

**01 Pinmux Simulation Verification**

**02 Pinmux Formal Verification**

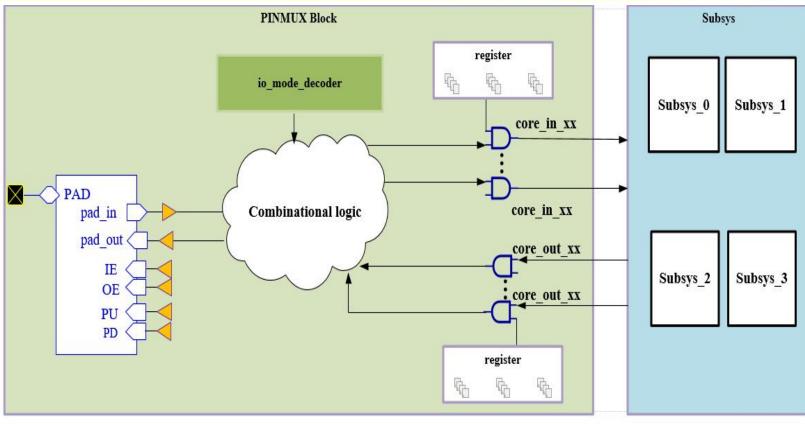

## Pinmux Design Architecture

**Design Feature:** 1) PAD cell: instance pad model Mode decoder: various mode confirmed ③Combinational logic: logic selection with basic logic gates 4 Registers: control of pullup/pull-down, sleep mode, and ie/oe enable

#### Verification plan:

a) Block Level: Check the connection between PAD and core inside PINMUXb) Soc Level: the connections between PINMUX and subsystems within the SoC

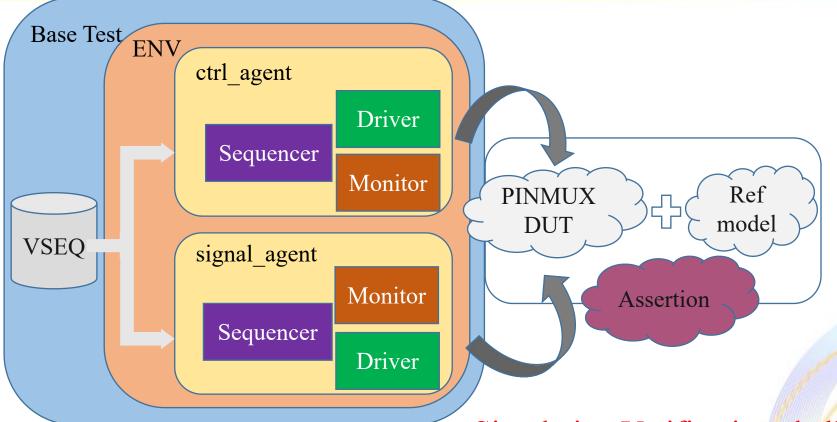

### Simulation Verification Solution

- I. ctrl\_agent: configure the PINMUX module to a specific operational modeII. signal\_agent: generate data

- transactions; III. Assertion: checks the

- reference signal and DUT output;(automatically generated by python)

#### Simulation Verification challenges:

- 1. A single simulation cannot exhaustively cover all incentives, need a large number of random test cases;

- 2. Coverage collected is time-consuming and inefficient with random transactions (now simAI can help)

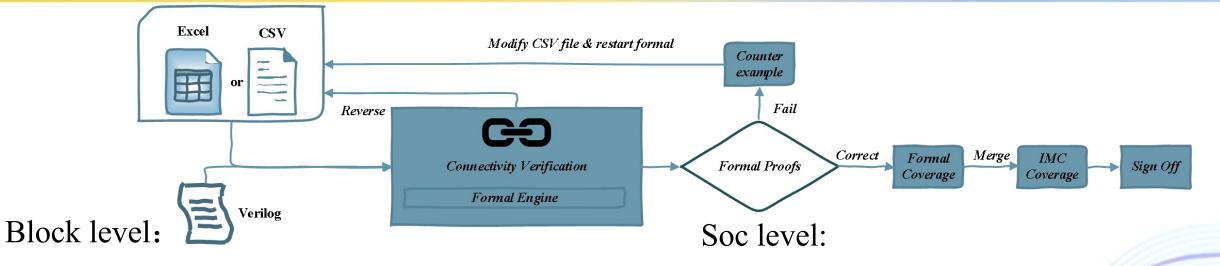

## **Formal Verification Solution**

- Excel sheet or a comma-separated-value (CSV) file; The generation of csv files is fully automated by python script;

- wire reverse extraction from analyzed and compiled RTL, directly output an Excel file or csv for review

≻ Register-Transfer Level (RTL)

check\_conn -reverse -src {pinmux} -dest {subsys\_0} -complexity (straightforward | simple | conditional | complex) -save\_as reverse.csv

#### 1 NAME, SRC BLOCK, SRC SIGNAL, DEST BLOCK, DEST SIGNAL

2 CONNECTION, a\_0,chip\_top,GPIO\_xx, IO\_MUX\_CORE, core\_in\_xx

3,COND\_EXPR, ptest==1&&PAD\_xx==0

CHINA

(ptest==1&&PAD\_XX==0) |-> (chip\_top.GPIO\_xx == IO\_MUX\_CORE.core\_in\_xx)

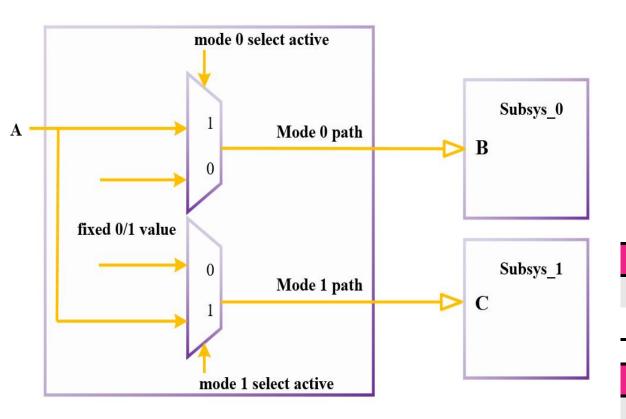

### **Pinmux Verification Completeness**

a single PAD has input functions across multiple modes, the CSV for one input function must reflect checks for fixed values of signals under other modes

1 NAME, SRC BLOCK, SRC SIGNAL, DEST BLOCK, DEST SIGNAL

2 CONNECTION, b\_0, chip\_top, A, Subsys\_0, B

3,COND\_EXPR, mode 0 = 1 && mode 1=0

#### **1 NAME, SRC BLOCK, SRC SIGNAL, DEST BLOCK, DEST SIGNAL**

2 CONNECTION, b\_1,chip\_top,A, Subsys\_1, 0

3,COND\_EXPR, mode 0 = 1 && mode 1=0

CHINA

e 33

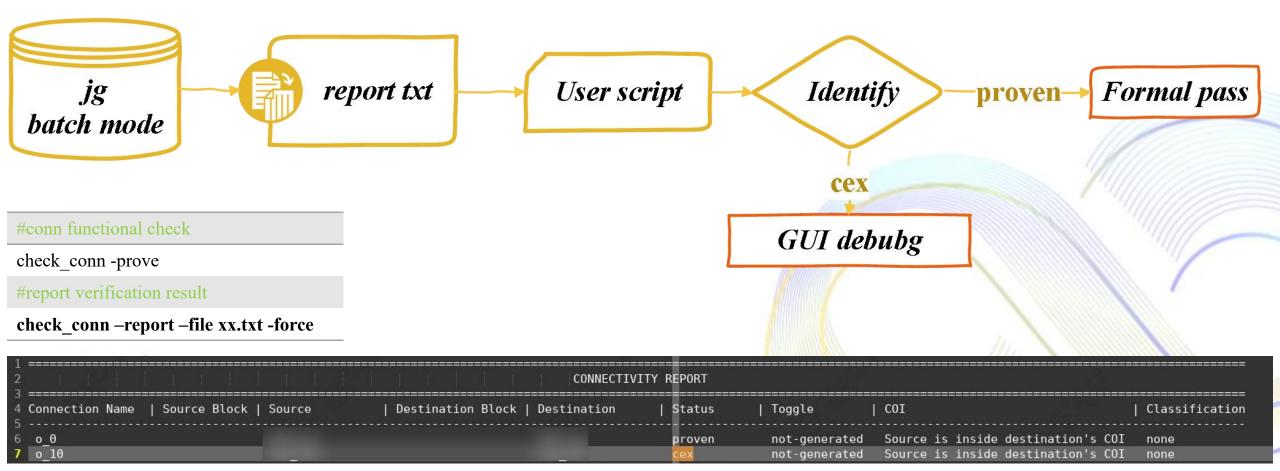

### Formal Prove Result

|                                                                          | ectivity V  | sign <u>A</u> pplication <u>W</u> indow <u>H</u> elp<br><b>'eri</b> Coverage – | d <sup>2</sup>                      | d <sup>2</sup> | de <sup>2</sup>    |          |                                  | dî                     | cāden<br>2/(2) 💿 🌀           |

|--------------------------------------------------------------------------|-------------|--------------------------------------------------------------------------------|-------------------------------------|----------------|--------------------|----------|----------------------------------|------------------------|------------------------------|

| File                                                                     | Desig       | gn Setup-Conn. Setup-Formal V                                                  | erification Search                  |                |                    |          |                                  |                        |                              |

|                                                                          |             |                                                                                | O 🐼 M ▼ 🗣 Search the Message        | Log            |                    |          |                                  |                        |                              |

| onnectivity                                                              | ty Viewer   |                                                                                |                                     |                |                    | X Tas    | k/Property Table                 |                        |                              |

| Worksheet                                                                | et Browser  | Connections Table                                                              |                                     |                |                    | Na       | me                               | Result                 | 2.2.2                        |

| 7*                                                                       |             |                                                                                |                                     |                | 8                  |          | All Tasks                        |                        |                              |

| Togo                                                                     | gle COI     |                                                                                |                                     | Destination    | Classification     | <b>_</b> | <pre><embedded></embedded></pre> | 0:0:0:0                |                              |

| 1095                                                                     | <u>s</u> ,c | p_1                                                                            |                                     |                | partial equal name |          | Connectivity                     | 36:0:0:0               |                              |

| 1                                                                        |             | p_2                                                                            |                                     |                | partial equal name |          |                                  |                        |                              |

| 1                                                                        |             | p_3                                                                            |                                     |                | partial equal name |          | 10                               |                        | 2011 PC:000705               |

| 1                                                                        | Ar          | p_4                                                                            |                                     |                | partial equal name | 8        | ኛ 🔞 No filter                    | ▼ Filter on name       | a.b 🖬 P 🔻                    |

| 1                                                                        | A           | p_5                                                                            |                                     |                | partial equal name |          | Type 5                           | P Name                 | ♥ Engine <sup>1</sup>        |

| 1                                                                        | Ar          | p_6                                                                            |                                     |                | partial equal name |          | Assert                           | conn:p 1               | Ht (1)                       |

| 1                                                                        | A           | p_7                                                                            |                                     |                | partial equal name | -  ~     | Assert                           | conn:p 2               | N (2)                        |

| 1                                                                        | A           | p_8                                                                            |                                     |                | none               |          | Assert                           | conn:p_3               | PRE (1)                      |

| /                                                                        | A           | p_9                                                                            |                                     |                | partial equal name | ×        | Assert                           | conn:p 4               | N (2)                        |

| 1                                                                        | Ar          | p_10                                                                           |                                     |                | partial equal name | 1        | Assert                           | conn:p_5               | N (2)                        |

| /                                                                        | Ar          | p_11                                                                           |                                     |                | partial equal name |          | Assert                           | conn:p_6               | N (2)                        |

| A                                                                        |             |                                                                                | 5.013                               | 9.015          |                    |          | Assert                           | conn:p_7               | N (2)                        |

| sessio                                                                   | -           |                                                                                |                                     |                | 00 🛤 - 🦉 👘         | 12 🗸     | Assert                           | conn:p_8               | PRE (1)                      |

|                                                                          |             | 02: INFO (ICOV030): Completed me                                               | asure for task {Connectivity}.      |                |                    | ▲ 🗸      | Assert                           | conn:p_9               | N (2)                        |

|                                                                          | vity] %     | # ## save coverage database                                                    |                                     |                |                    | 1        | Assert                           | conn:p_10              | Ht (1)                       |

| Connectivity] % # check cov -save ./cov db/cov.\${conn target}.db -force |             |                                                                                |                                     |                |                    | 1        | Assert                           | conn:p_11              | Ht (1)                       |

| Connecti                                                                 |             |                                                                                |                                     |                |                    | 1        | Assert                           | conn:p_12              | N (2)                        |

|                                                                          | vity] %     | set time end [tcl clock seconds]                                               |                                     |                |                    | ×        | Assert                           | conn:p_13              | N (2)                        |

| 74367392                                                                 |             | set time end [tet ctock seconds]                                               |                                     |                |                    | <b>v</b> | Assert                           | conn:p_14              | N (2)                        |

|                                                                          |             |                                                                                | [expr \$time end - \$time start] se | econds"        |                    | ×.       | Assert                           | conn:p_15              | N (2)                        |

|                                                                          | O] Total    | Time : 435 seconds                                                             |                                     |                |                    | 1        | Assert                           | conn:p_16              | N (2)                        |

| onnecti                                                                  | rarrh 1 .0  |                                                                                |                                     |                |                    | -        | Assert                           | conn:p_17              | N (2)                        |

|                                                                          |             |                                                                                |                                     |                |                    | ≓ ∕      | Assert                           | conn:p_18              | N (2)                        |

| Connecti                                                                 | lvity] %    |                                                                                |                                     |                |                    | 1        | Cover (related)                  | conn:p_1:precondition1 | Нр                           |

|                                                                          |             |                                                                                |                                     |                |                    | 1        | Cover (related)                  | conn:p_2:precondition1 | Нр                           |

|                                                                          | LinkMar     | enges Margings / France Proof                                                  | lassagas                            |                |                    |          |                                  | - 1- 1-                |                              |

| Console                                                                  | Lint Mess   | sages Warnings / Errors Proof M                                                | lessages                            |                | A 20               | 旧  Tota  | al: 37 Filtered: 3               |                        | alidity: 36:0:0:1 Run: 1:0:0 |

|                                                                          |             |                                                                                |                                     |                |                    |          |                                  | No proofs running      | Console input ready          |

| T                                                                        | oggle C     | 07 Connection Name                                                             | Source                              |                | Destination        |          |                                  |                        |                              |

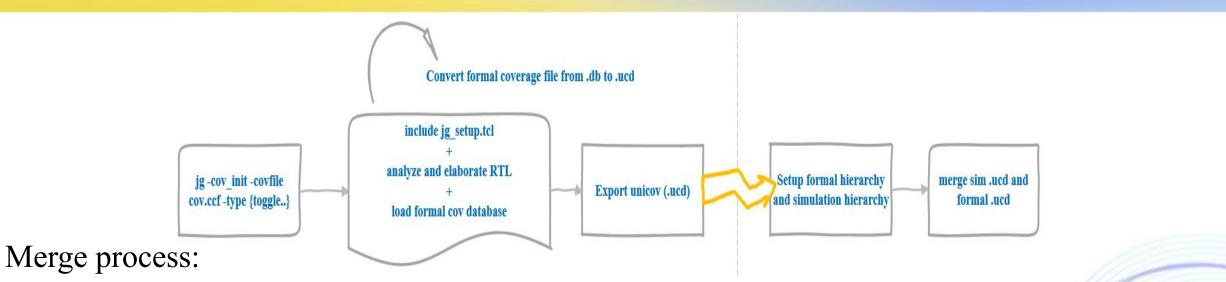

- First, convert formal's .db to .ucd; (database -export\_unicov)

- 2. Specify source (formal\_top) and target

(sim\_top)

- 3. merge /sim\_cov/cov /formal/cov/

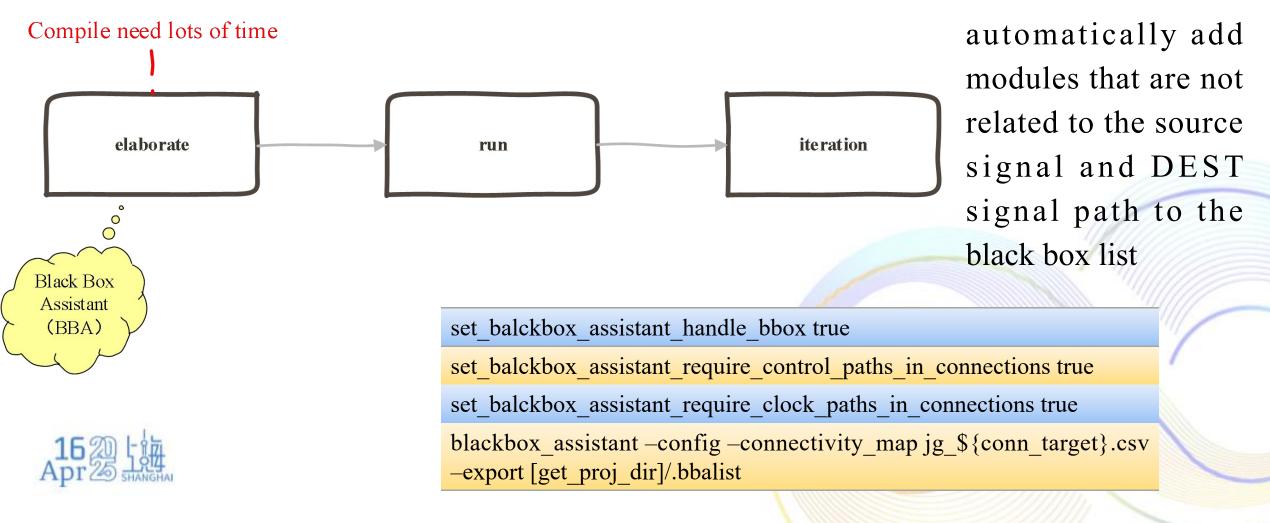

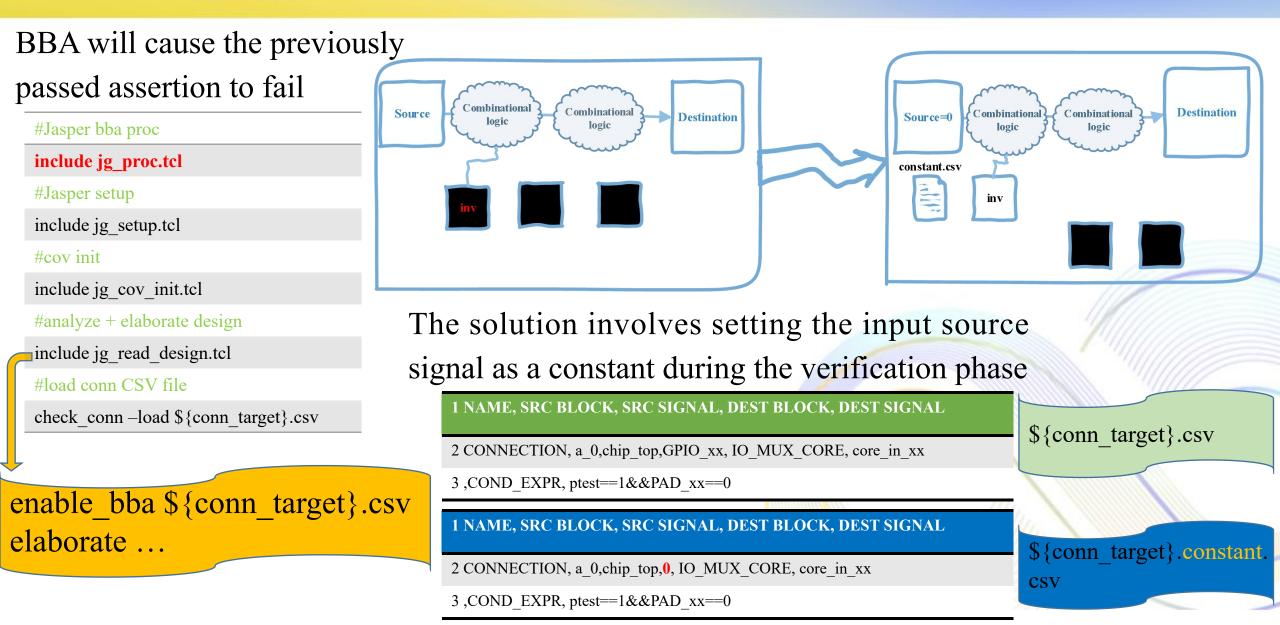

#### 1. BBA

2025

CHINA

#### 2. Parallel verification

#### a template tcl and leverage the bsub command for execution;

#### clear –all

set time\_start [tcl\_clock seconds]

set conn target CONN TARGET

#### #Jasper setup

include jg\_setup.tcl

#### #cov init

include jg\_cov\_init.tcl

#analyze + elaborate design

include jg\_read\_design.tcl

#load conn CSV file

check\_conn -load ./csv/\${conn\_target}.csv

#clock and reset

clock -none

reset -none

#### #include conn constraints

include ./cons/cons.\${conn\_target}.tcl

#conn structural check

$check\_conn\ -validate$

#conn functional check

$check\_conn\ \text{-}prove$

#switch tab to Connectivity

check\_cov -configure\_gui -task Connectivity

#coverage measurement

check\_cov -measure -task Connectivity

#save coverage database

check\_cov save ./cov\_db/cov.\${conn\_target}.db force

set time end [tcl clock seconds]

- 3. accelerate the convergence of results

- identify the formal verification tool has fully proven the design in batch mode

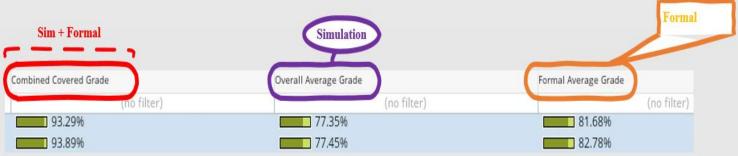

## **Formal & Simulation Comparison**

CHINA

SYSTEMS INITIATIVE

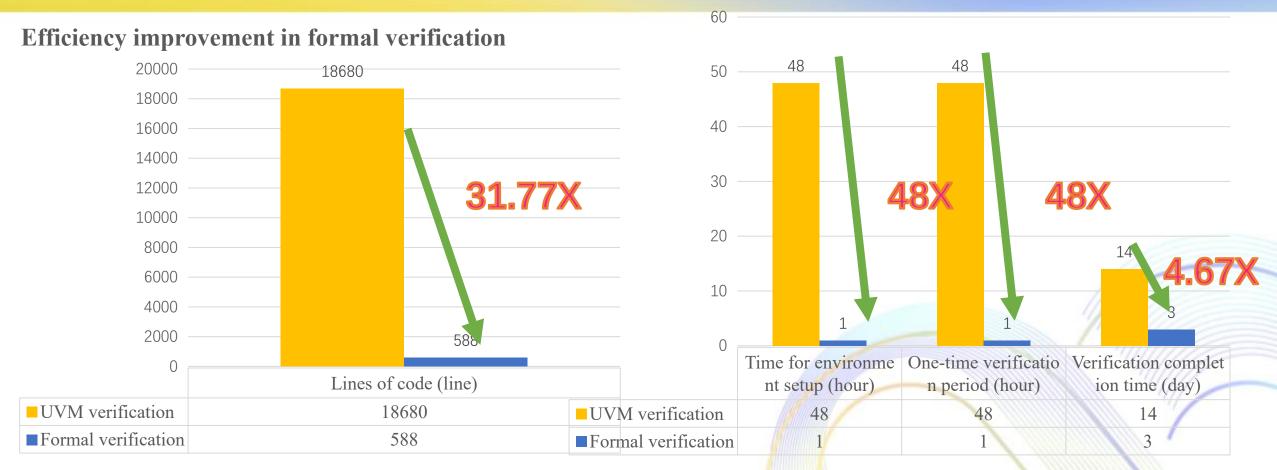

Formal streamlines the 10,000+ lines of code to just 588 lines;

Time required for environment setup and a single formal verification within an hour;

Formal verification complete the whole verification in merely three days.

# THANKS

This document to for informational purposes only and the data and information contained in it do not represent any form (express or implied) of warranty or commitment, and the views or conclusions expressed in this document do not constitute any advice. UNISOC reserves the right to make any changes to this document without prior notice. Under no circumstances shall UNISOC be liable for any direct or indirect damage or loss related to the document. The data and information contained in this document are the confidential information and property of UNISOC and/or its lignesors . You may not use, copy or distribute any part of this document without prior consent of UNISOC.