# Automated SVA Generation with LLMs

Lik Tung Fu, School of Integrate Circuits, Southeast University, Nanjing, China, (liktungfu@seu.edu.en)

Shaokai Ren, National Center of Technology Innovation for Electronic Design Automation, Nanjing, China, (renshaokai@nctieda.com)

Mengli Zhang, National Center of Technology Innovation for Electronic Design Automation, Nanjing, China, (zhangmengli@nctieda.com)

Sichao Yang, X-EPIC Corporation Limited, Shanghai, China, (sichaoy@x-epic.com)

Ruiming Zeng, X-EPIC Corporation Limited, Shanghai, China, (raymondz@x-epic.com)

Zhe Jiang, School of Integrate Circuits, Southeast University, Nanjing, China, (101013615@seu.edu.cn) Xi Wang, School of Integrate Circuits, Southeast University, Nanjing, China, (*xi.wang@seu.edu.cn*) Jun Yang, School of Integrate Circuits, Southeast University, Nanjing, China, (*dragon@seu.edu.cn*)

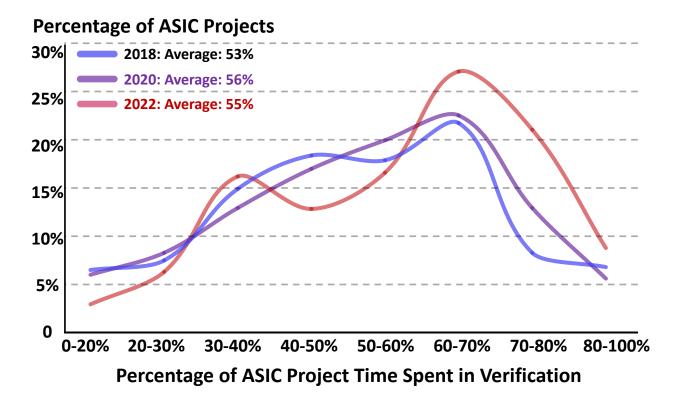

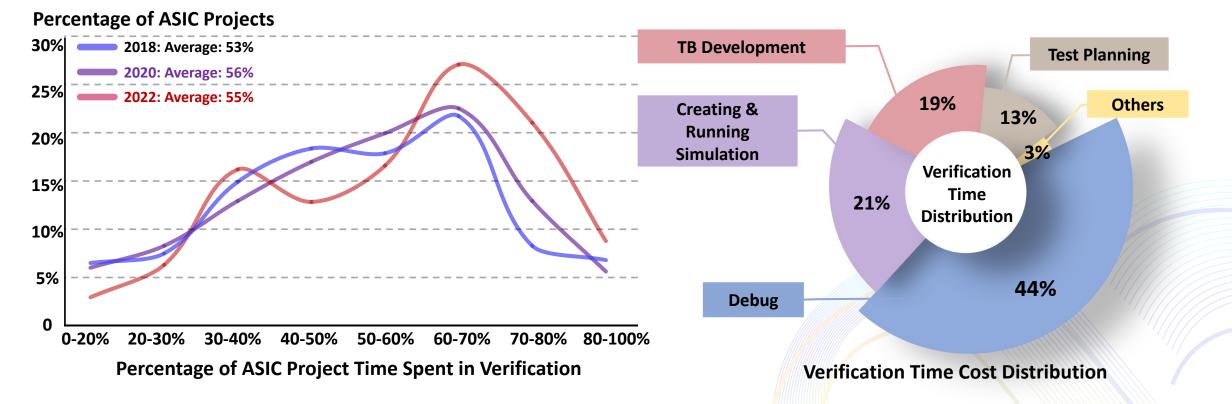

- Verification accounts for over **50%** development time.

- The engineer ratio of design to verification ranges from 1:2 to 1:3.

- Verification accounts for over **50%** development time.

- The engineer ratio of design to verification ranges from 1:2 to 1:3.

•

3

**Debugging dominates the verification process.**

When the posedge of signal <clk> is detected and reset signal <rstn> is active, if <rstn> rises, then implies <vld\_out> equals to 1-bit binary number 0.

```

property vld_out_reset;

@(posedge clk) disable iff(!rstn) $rose(rstn)|-> vld_out == 1'b0;

endproperty

Assert_vld_out_reset:assert property (vld_out_reset) else $error(" unexpected <vld_out> reset

behavior ")

```

15 SVA (SystemVerilog Assertions) specifies the expected behavior under predefined conditions and captures potential errors through real-time verification of their correctness.

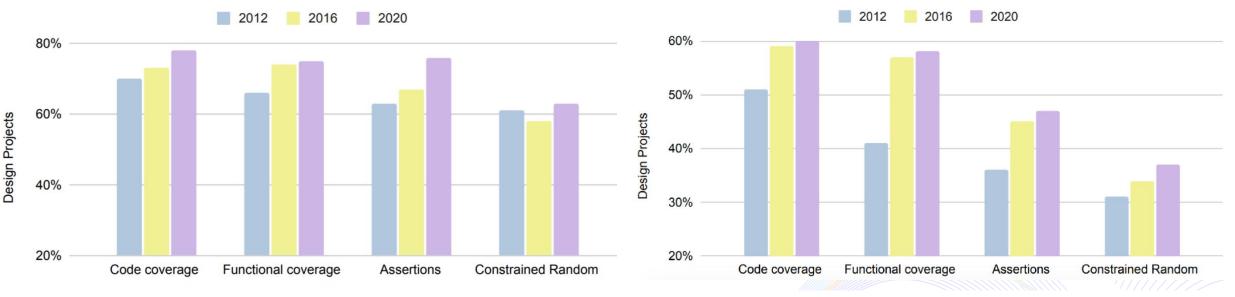

**Assertion Based Verification**

## **Advantage of Assertion:**

- Early-Stage Error Detection

- Observability

- maintainability

#### **Assertion Based Verification**

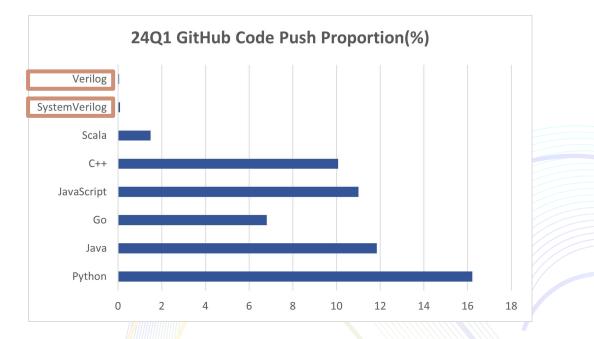

ASIC functional verification trend

FPGA functional verification trend

## However, SVA writing is labor-intensive and error-prone, agile SVA Generation is highly needed.

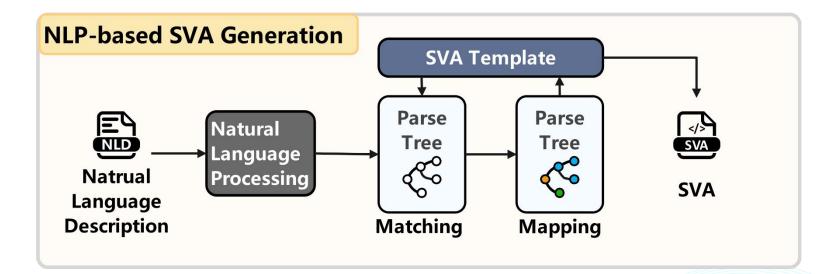

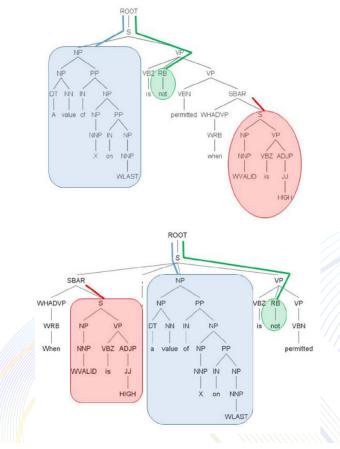

NLP-based approaches aim to develop translators that convert natural language verification requirements into SVA code. Early approach employed NLP techniques to parse SVA natural language descriptions into parse trees. These trees are then structurally matched to SVA templates, with key components like **signals**, **conditions**, and **actions** being automatically segmented. Finally, predefined mapping rules populate these modular components into template slots to generate SVA assertions.

## **Disadvantages :**

- Low generalization ability

- Limited abstraction-level of input

- Poor generative ability when faced with complex descriptions

The parse trees of two sentences with the same meaning but different expressions.[1]

[1] J. Zhao and I. G. Harris, "Automatic assertion generation from natural language specifications using subtree analysis," in 2019 Design, Automation Test in Europe Conference Exhibition (DATE), 2019, pp. 598–601.

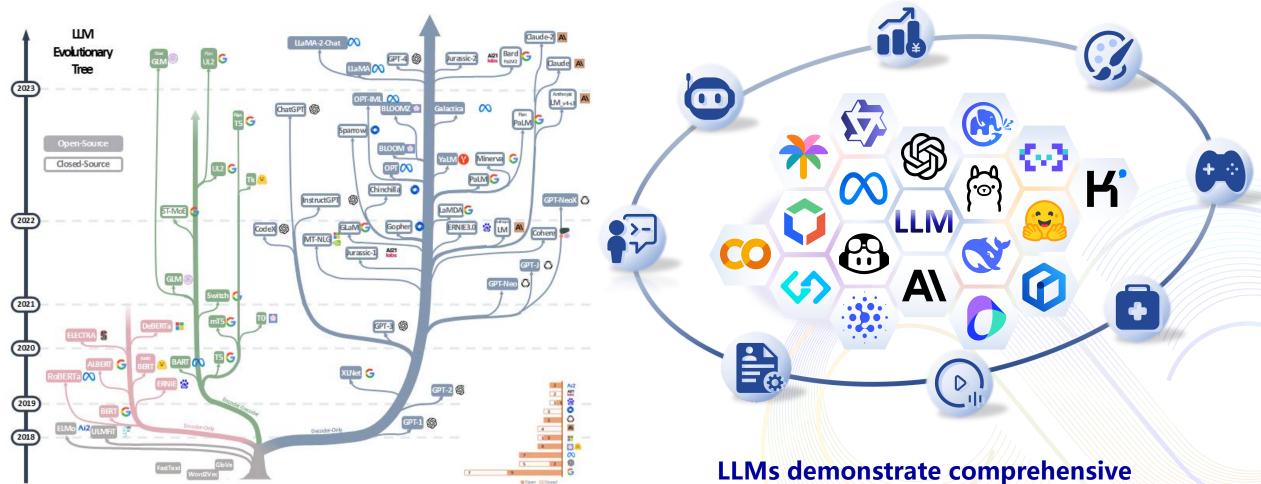

intelligent and automated capabilities.

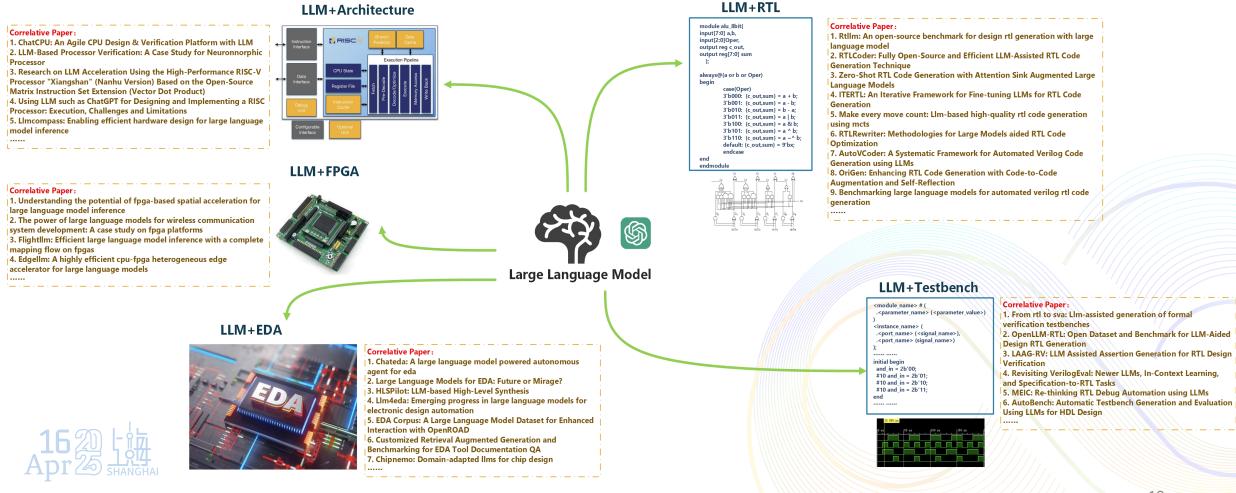

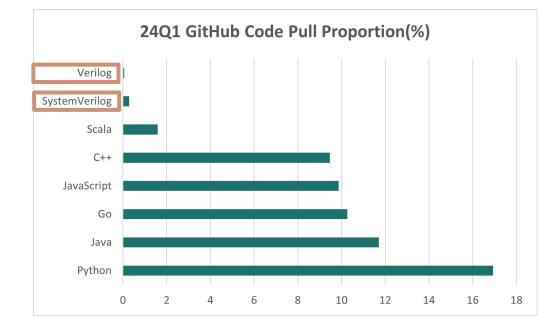

#### **LLM in HDL Generation**

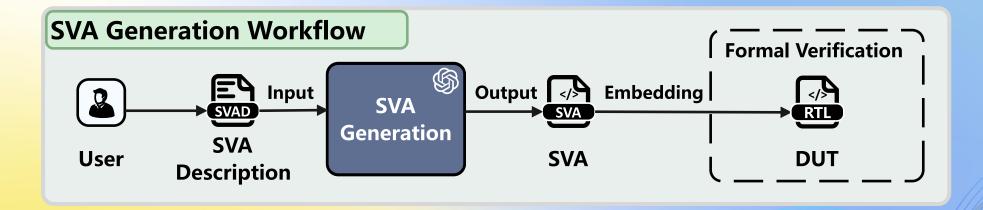

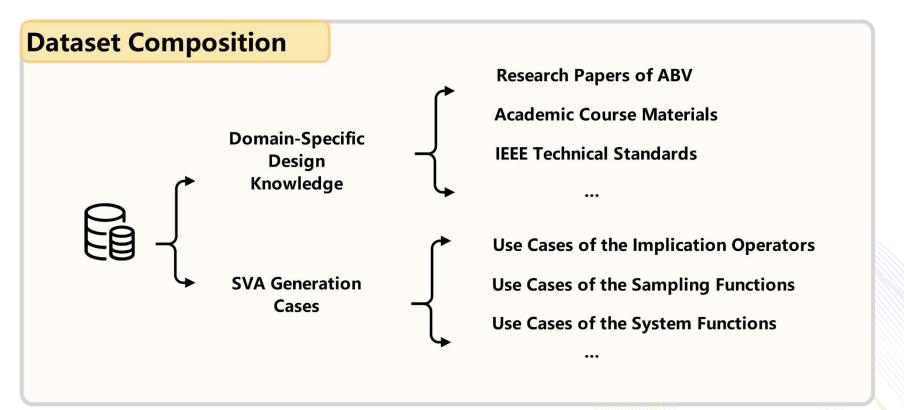

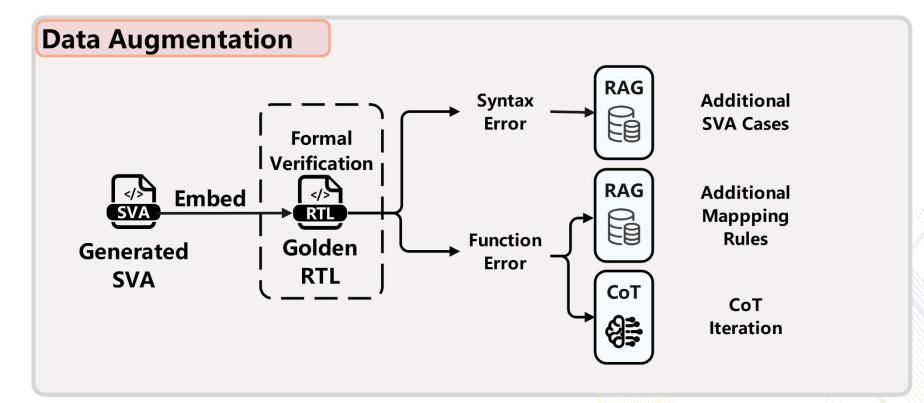

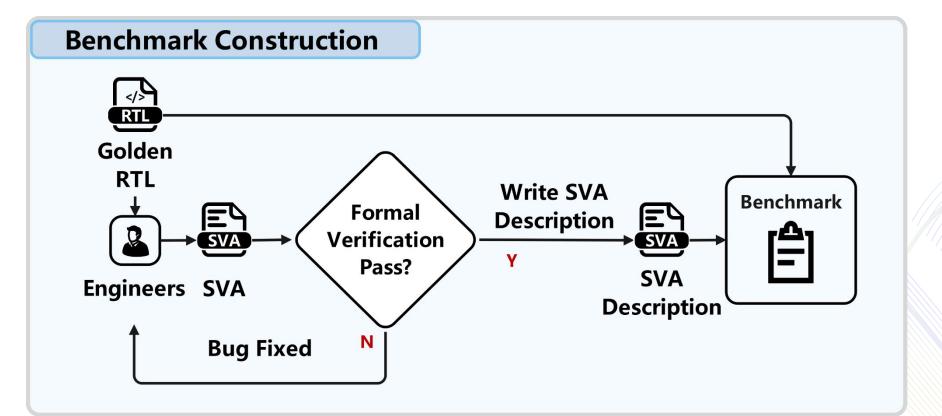

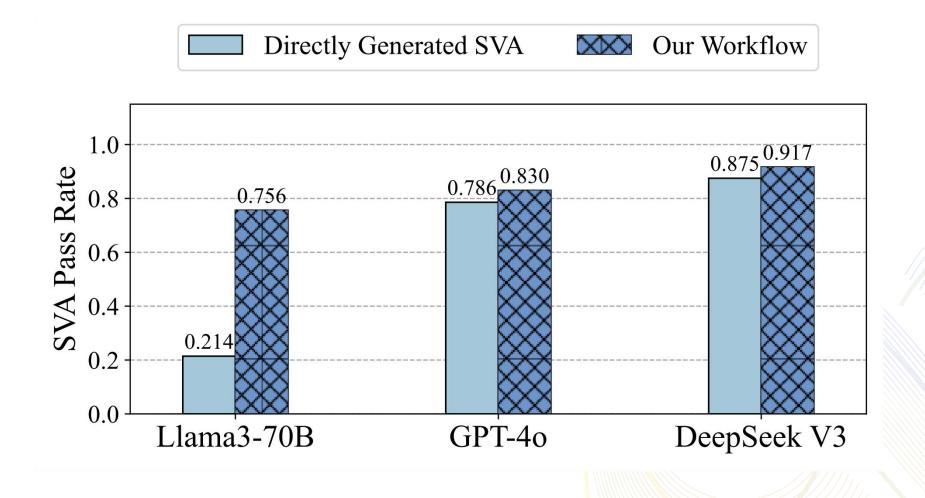

We designed an end-to-end automated generation system from SVA descriptions to SVAs, a LLM combined with customized Chain of Thought (CoT) and Retrieval-Augmented Generation (RAG), achieving high-quality SVA generation.

| Situation                      | Example Input                                                                                                                                                                                                                                                                                                                                                                                                       | Expected Output                                                                                             | Correctness of<br>DeepSeek V3 with<br>RAG+CoT |

|--------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------|-----------------------------------------------|

| Complex Logic<br>Nesting       | When the posedge of signal <clk> is triggered, the result of the reduce and of not <init_state> and <a> should be true. where <a> is the reduce and of <cld_we_1> and the result of <ic_ram[{old_adr, 3'b001}]=""> equal to the 23rd to 16th bit of <old_di>.</old_di></ic_ram[{old_adr,></cld_we_1></a></a></init_state></clk>                                                                                     | <pre>@(posedge clk) (~init_state &amp; (old_we_1 &amp; (ic_ram[{old_adr, 3'b001}] == old_di[23:16])))</pre> | 75%                                           |

| Complex Temporal<br>Expression | When the posedge of signal <wb_clk_i> is triggered<br/>and the signal <wb_rst_i> is not active, if<br/><wb_cyc_i> and <wb_std_i> both rise, then it<br/>implies nonoverlappingly that the negation of the<br/>value of <wb_ack_o> at past 1 cycle is true for at<br/>least 1 cycle is true, and <wb_ack_o> should be low<br/>1 clock cycle later.</wb_ack_o></wb_ack_o></wb_std_i></wb_cyc_i></wb_rst_i></wb_clk_i> | <pre>@(posedge wb_clk_i) disable iff(wb_rst_i) \$rose(wb_cyc_i &amp;&amp; wb_std_i)  =&gt;</pre>            | <b>60%</b>                                    |

#### **Template of SVA Description:**

We imposed no restrictions on sentence structure or phrasing during dataset construction, though designers naturally exhibit preferred phrasing tendencies. Leveraging LLMs' strong generalization capabilities, simply introducing new cases into the RAG framework enhances their parsing accuracy for novel expressions.

#### **Ensuring Accuracy of LLM-Generated SVA:**

Current LLM-based automated SVA generation remains an assistive tool. Engineers must verify the correctness of generated assertions and employ iterative dialog refinement to obtain functionally valid SVAs.

#### **Future Outlook:**

This research demonstrates the significant enhancement of LLM assertion generation capabilities through the RAG+CoT framework, particularly when leveraging large-scale datasets. As generation strategies become more refined, verification-specific datasets expand, and LLMs evolve to the next generation, assertion pass rates will progressively increase. This advancement will enable assertion-based verification with substantially reduced engineering effort.

# **Thanks for listening!**