## A Multi-Agent Generative AI Framework for IC Module-Level Verification Automation

Wenbo Liu, wenbo.liu@jaguarmicro.com Forbes Hou, forbes.hou@jaguarmicro.com Jon Zhang, jon.zhang@jaguarmicro.com Hong Liu, hong.liu@jaguarmicro.com Allen Lei, allen.lei@jaguarmicro.com IC Design Department, Jaguar Microsystems

### 云豹智能——中国数据处理器芯片(DPU) 头部企业

- 1. Limitations and Opptunites of Traditional Verification Methods

- 2. Multi-Agent Verification Framework

- 3. Comparative Demonstration

- 4. Evaluation

- 5. Discussion

- 6. Q&A

## 1. Limitations of Traditional Verification Methods

#### **accellera** SYSTEMS INITIATIVE 1. Limitations and Opportunities of Traditional Verification Methods

| Phase                  | Traditional Approach                      | Intelligent Approach                 |  |  |  |

|------------------------|-------------------------------------------|--------------------------------------|--|--|--|

| Specification Analysis | Manual Analysis                           | Auto-generation + Manual Calibration |  |  |  |

| Verification Planning  | Manual Analysis                           | Auto-generation + Manual Calibration |  |  |  |

| Environment Setup      | Framework Auto-generation + Manual Coding | Auto-generation + Manual Calibration |  |  |  |

TABLE I

Comparison between Traditional Verification Methods and Intelligent Verification Methods

- New Technical Trends

- Multimodal Parsing

- RAG Integrates Domain

- Knowlage

- Multi-Agent Systems 15 20 - 17 Apr 25 SHANGHAI

- Al Verification Application

- Opportunities

- Design specification processing

- Testbench construction

- Methodological innovation

Challenges

simple conversational

approaches struggle to

address such complex

problems.

•

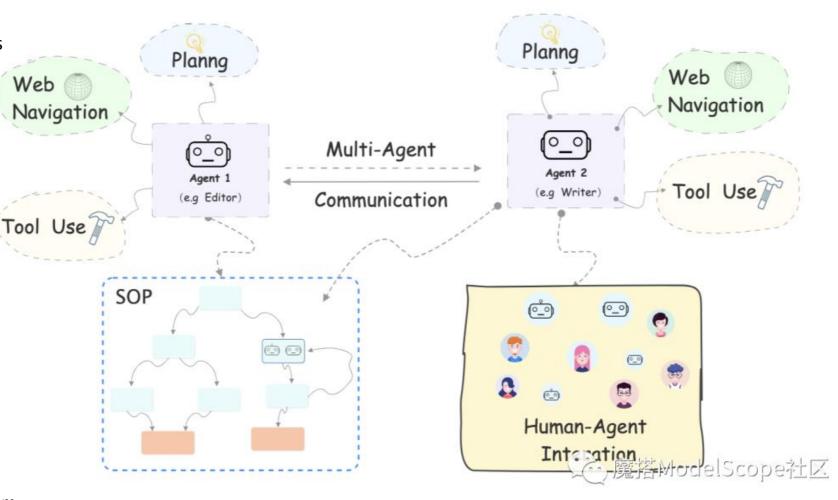

# 2. MAVF - Multi-Agent Verification Framework

- Core Features:

- Process Stability: Integrates industry SOPs to achieve precise domain knowledge mapping, ensuring output consistency

- Role Specialization: Differentiated intelligent agent role configurations, building systematic solutions

### • System Modules:

- Distributed Multi-Agent Architecture

- Unified Interaction Environment Platform

- Standardized Process Control Protocol

- Quality Verification System

- Intelligent Routing Communication Mechanism

- Event Subscription Response Mechanism

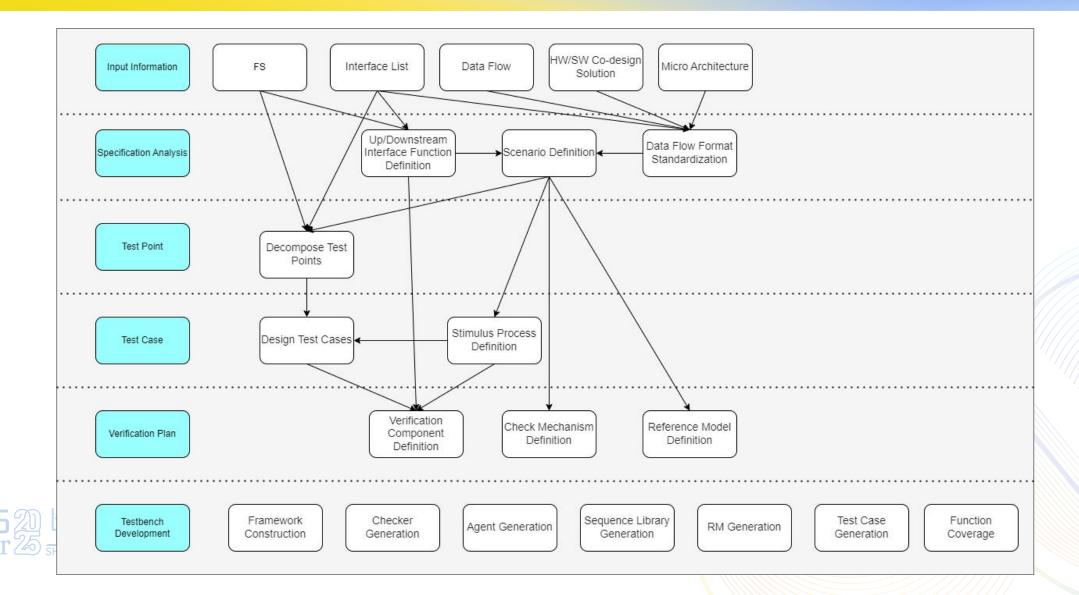

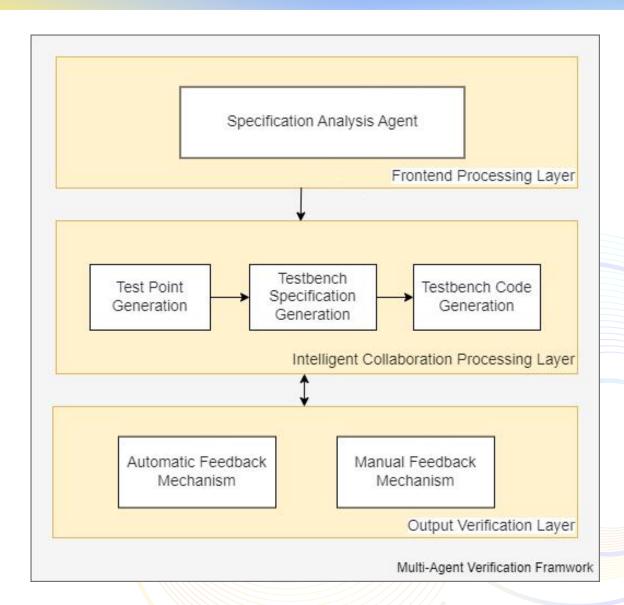

## 2. MAVF : Module-Level Verification Flow Analysis

- Frontend Processing Layer

- Implements unified structural conversion of multi-modal design documents, generating standardized design specification libraries through normative parsing agents according to sub-SOPs, providing a unified input source for downstream processes.

- Agent Collaboration Layer

- Implements three-stage collaboration based on workflow engineEach agent strictly follows the main SOP process, triggering downstream tasks through phase acceptance

- Closed-loop Verification Layer

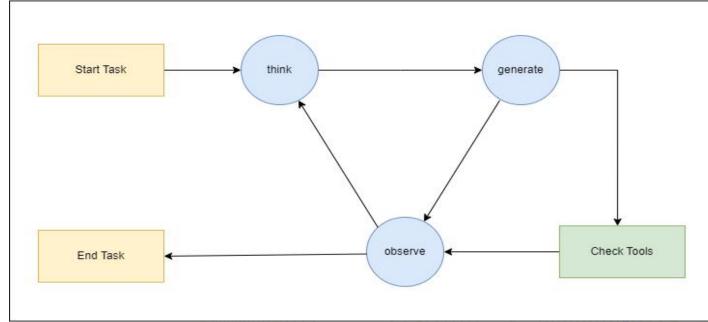

• Adopts ReAct chain of thought to implement:Forms an automated quality loop of planning-execution-verification

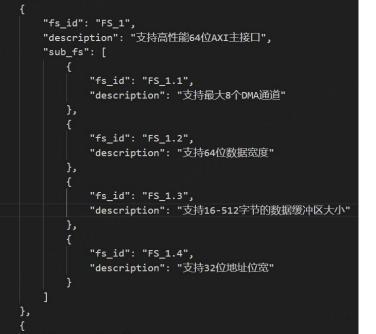

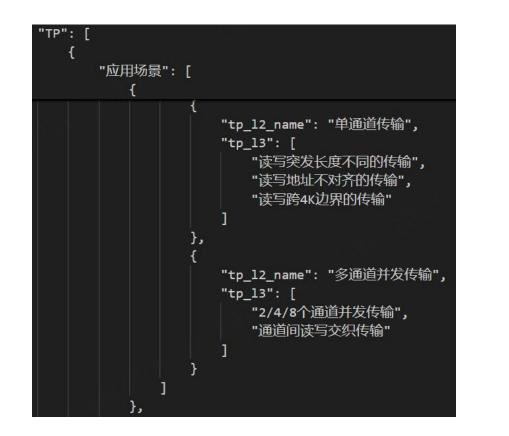

- A. Specification Parsing Agent

- Input Processing Standardize document formats

- Information Extraction

- Output Integration JSON template

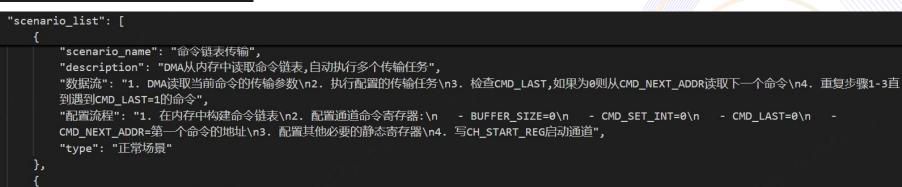

- B. Verification Plan Generation Agent

- Test point decomposition

- Test case generation

- Inspection mechanism

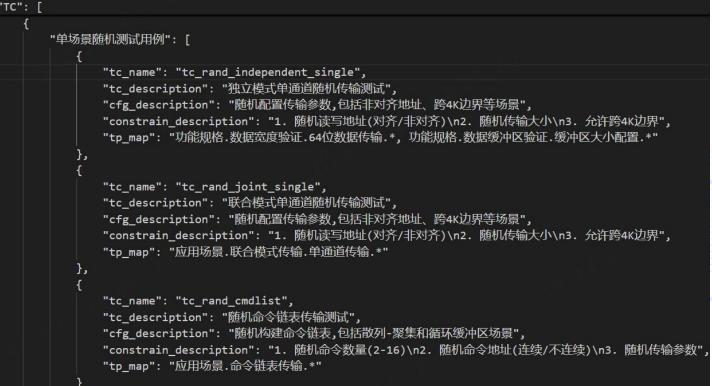

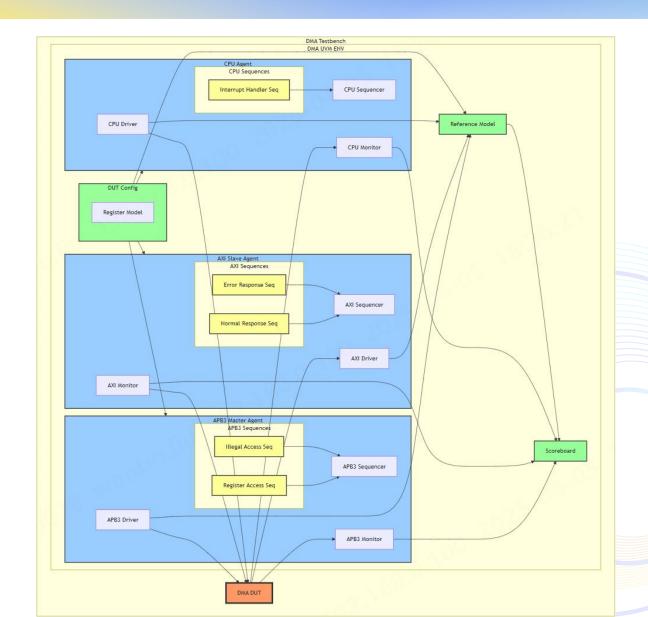

- C. Testbench Spec Generation Agent

- Establishing the testbench architecture and creating a topological diagram

- Determining the functionality, quantity, and hierarchical relationships between verification components

- Providing specific definitions for core data structures and driving

functions within components

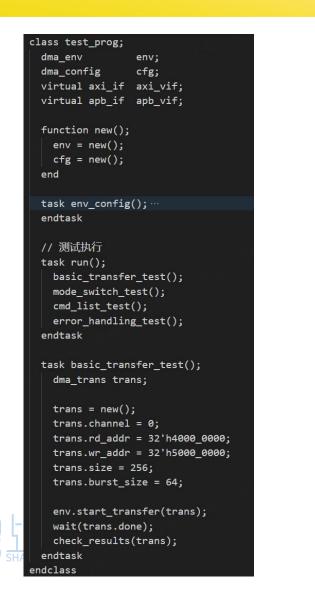

- D. Testbench Code Generation Agent

- Framework Level (UVM Architecture)

- Transaction Level (Data Flow)

- Scenario Level (Test Cases)

- Industry Compatibility

云 豹智能

- Dynamic Verification Cycle

- AI Generation → Automated Review → Human

Confirmation

- Cyclic Iteration Until Standards Are Met

- Multi-dimensional Consistency Checking System

- Verification Planning Phase Orthogonal Coverage Verification/Scenario Completeness Validation

- Testbench Generation Phase

- Al Semantic Check (Grammar + Functional)

- Manual Review (Architecture

Rationality/Completeness of Checking

Mechanisms)

• Execution Feedback Phase

• EDA Tools Log Review

- Human-Machine Collaboration Principles

- Quality Loop: Automated pre-screening  $\rightarrow$  Expert review

- Trustworthy AI Mechanism

- Establish traceable generation-verification evidence chains

• Enhanced assistance tool, not a replacement for human work

SYSTEMS INITIATIVE

"fs\_id": "FS\_2",

2025

DESIGN AND VERIFICATION"

CONFERENCE AND EXHIBITION

"FS": [

## accellera

## 2. MAVF : Verification Plan Generation Agent

### **2. MAVF**: Testbench Specification Agent

[verif\_components\_hierarchy] DMA Testbench DMA UVM ENV CPU Agen **CPU** Sequences "ТВ": { "interface": [ ··· Interrupt Handler Seq **CPU** Sequencer ], "top\_tb": [ CPU Driver Reference Model CPU Monitor "item": "dma tb top", "item\_description": "顶层testbench,实例化DUT、接口和test", "reuse": "no" DUT Config }, Register Model "item": "clk\_rst\_gen", "item\_description": "时钟复位生成模块", AXI Slave Agen **AXI** Sequences "reuse": "yes" Error Response Seq ], AXI Sequencer "test": [ Normal Response Seq "env": [ AXI Driver "agent name": "apb3 agent", AXI Monitor "agent\_description": "APB3配置接口代理,负责寄存器配置访问", "agent\_type": "master", PB3 Master Agent APB3 Sequences "agent\_sequence\_description": "实现寄存器读写、非法访问等场景", "agent\_interface": "连接DUT的APB3从接口", Illegal Access Seq Scoreboard "reuse": "vip" APB3 Sequencer }, Register Access Sec "agent\_name": "axi\_agent", APB3 Driver "agent\_description": "AXI数据传输接口代理,负责数据传输", APB3 Monitor "agent\_type": "slave", "agent\_sequence\_description": "实现正常传输、错误响应等场景",

DMA DUT

## 2. MAVF : Testbench Code Generation Agent

dma verif/

- env/

- dma env.sv

- dma env cfg.sv

- dma env pkg.sv

- dma reference model.sv

- dma scoreboard.sv

- L— dma\_virtual\_sequencer.sv

- ral/

- └── dma ral\_pkg.sv /\* RAL model \*/ agents/

- cpu agent/ /\* user defined Agent \*/

- cpu\_agent.sv

- cpu driver.sv

- cpu\_monitor.sv

- cpu sequencer.sv

- cpu seg item.sv

- cpu pkg.sv

- apb3\_agent/ /\* Synopsys VIP \*/

- axi pkg.sv

- sequences/

- └── dma\_seq\_pkg.sv

- tests/

- dma base test.sv

- dma\_test\_lib.sv

- └── dma test pkg.sv

- tb/

- dma tb top.sv

- dma clk rst if.sv

- - Makefile

- run.f

- - └── apb3\_pkg.sv

- └── axi\_agent/ /\* Synopsys VIP \*/

- dma\_virtual\_seq.sv

- dma\_seq\_lib.sv

- dma\_apb3\_if.sv

- └── dma axi if.sv

- sim/

class dma env extends uvm env;

virtual function void connect phase(uvm phase phase); // Connect register model

- reg\_model.default\_map.set\_sequencer(apb3\_agt.sequencer, reg2apb); reg model.default map.set auto predict(1);

- // Connect virtual sequencer vseqr.apb3\_sqr = apb3\_agt.sequencer; vseqr.axi sqr = axi agt.sequencer; vseqr.cpu\_sqr = cpu\_agt.sequencer; vseqr.reg model = reg model;

- // Connect monitors to reference model apb3\_agt.monitor.item\_collected\_port.connect(rm.apb\_analysis\_imp); cpu agt.monitor.item collected port.connect(rm.cpu analysis imp);

- // Connect monitors to scoreboard apb3\_agt.monitor.item\_collected\_port.connect(sb.apb\_analysis\_imp); axi agt.monitor.item collected port.connect(sb.axi analysis imp);

- // Connect reference model to scoreboard rm.predict\_ap.connect(sb.rm\_analysis\_imp);

- cpu\_agt.monitor.item\_collected\_port.connect(sb.cpu\_analysis\_imp);

- endfunction

write\_reg(reg\_model.CMD\_REG3[ch\_id], {next\_addr[31:4], last, set\_int});

- - // Send prediction to scoreboard

- class dma\_reference\_model extends uvm\_component; virtual function void predict transfer(apb seg item item);

- mem data trans predict trans; int channel\_id;

- // Extract channel ID and command info

- predict trans = mem data trans::type id::create("predict trans");

- channel id = get channel id(item.paddr); // Create prediction transaction

- // Handle different transfer modes if(channel\_status[channel\_id].joint\_mode) begin handle\_joint\_mode(channel\_id, predict\_trans);

- end else begin handle independent mode(channel id, predict trans); end

- // Handle command list mode if(cmd\_queue[channel\_id].cmd\_list\_mode) begin handle cmdlist(channel id, predict trans);

- end

- predict ap.write(predict trans); endfunction

class dma virtual sequence extends uvm sequence;

write reg(reg model.CMD REG0[ch id], rd addr);

write\_reg(reg\_model.CMD\_REG1[ch\_id], wr\_addr);

write\_reg(reg\_model.CMD\_REG2[ch\_id], size);

endtask

task config cmd(int ch id, bit[31:0] rd addr, bit[31:0] wr addr, int size, bit set int, bit last, bit[31:0] next addr); // contigure command registers

# 3. Comparative Demonstration

## 3. Comparative Demonstration – Test Plan Analysis ENDER

Table V ↔

Comparison of the effectiveness of Module\_A in two scenarios: fully automated execution in MAVF versus test point generation through conversational interaction with LLM. Due to space limitations, only partial content is presented.

|                                                                                                                                                           | MAVF 47                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Chat $_{\circ}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1<br>2<br>3<br>4<br>5<br>6<br>6<br>7<br>8<br>9<br>9<br>10<br>11<br>12<br>13<br>14<br>15<br>16<br>17<br>18<br>19<br>20<br>21<br>22<br>22<br>23<br>24<br>25 | MAVF &<br>"TP": [*'<br>{*'<br>"tp_l1_name": "Address Width Conversion Function",*'<br>"tp_l2": [*'<br>{*'<br>"tp_l3": [*'<br>"Supports S_ADDR_W bit configuration",*'<br>"tp_l3": [*'<br>"supports M_ADDR_W bit configuration",*'<br>]*'<br>},*'<br>{*'<br>"tp_l2_name": "Address Conversion Calculation<br>Test",*'<br>"tp_l3": [*'<br>"When window matches, output address =<br>{ext_addr, 20'd0} + axi_slave_addr - region_start_addr",*'<br>"When no window matches, output address =<br>{ext_addr, 20'd0} + axi_slave_addr - region_start_addr",*'<br>"When no window matches, output address =<br>{default_slave_address[M_ADDR_W-1:12],<br>axi_slave_addr[11:0]]"*'<br>]*'<br>},*'<br>{*'<br>"tp_l1_name": "Window Configuration Function",*'<br>"tp_l2": [*'<br>{*'<br>"tp_l2_name": "Window Quantity Configuration | <ul> <li>space limitations, only partial content is presented. <i>v</i></li> <li>Chat <i>v</i></li> <li>1 1. Address expansion functionality verification:<i>v</i></li> <li>2 (1) Verify that M7 (32-bit address bus) can correctly access N2 (48-bit address bus) address space through im_soc_remap.<i>v</i></li> <li>3 (2) Test address translation from 32-bit to 48-bit addresses.<i>v</i></li> <li>4 2. Window configuration verification:<i>v</i></li> <li>5 (1) Test different window quantity configurations (16, 32, 64).</li> <li>6 (2) Verify start and end address configuration for each window.</li> <li>7 (3) Test window enable/disable functionality (default disabled).<i>v</i></li> <li>8 (4) Verify 1MB minimum granularity for window addresses <i>v</i></li> </ul> |

| 26<br>27<br>28                                                                                                                                            | Test",+'<br>"tp_13": [+'<br>"Supports configuration of 1-64 windows",+'<br>"Register writes beyond the configured window                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 29<br>30<br>31<br>32                                                                                                                                      | count are invalid and read as 0"+'<br>]+'<br>},+'<br>{+'<br>"tp_l2_name": "Window Address Configuration<br>Test",+'                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 33<br>34                                                                                                                                                  | "tp_]3": [+'<br>"Start address and end address minimum<br>granularity is 1MB",+'                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 35<br>36<br>37<br>38<br>39<br>40                                                                                                                          | "Addresses must be 8-byte aligned",<br>}+<br>}+<br>}+<br>}+<br>}+                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

#### **accellera** 3. Comparative Demonstration – Testbench Architecture

## 3. Comparative Demonstration – Sequence

class test\_prog;

dma\_env env; dma\_config cfg; virtual axi\_if axi\_vif; virtual apb\_if apb\_vif;

function new(); env = new(); cfg = new(); end

task env\_config(); ...

endtask

// 测试执行

task run();

basic\_transfer\_test();

mode\_switch\_test();

cmd\_list\_test();

error\_handling\_test();

endtask

task basic\_transfer\_test();

dma\_trans trans;

trans = new(); trans.channel = 0; trans.rd\_addr = 32'h4000\_0000; trans.wr\_addr = 32'h5000\_0000; trans.size = 256; trans.burst\_size = 64;

env.start\_transfer(trans);

wait(trans.done);

check\_results(trans);

endtask

endclass

class dma\_cmdlist\_seq extends uvm\_sequence #(axi\_slave\_transaction); `uvm\_object\_utils(dma\_cmdlist\_seq)

rand int channel = 0; bit[31:0] cmd\_list[5];

function new(string name="dma\_cmdlist\_seq"); super.new(name); initialize\_cmd\_list(); endfunction

virtual task body(); setup\_command\_list(); start\_dma\_transfer(); wait\_for\_interrupt(); endtask

virtual task setup\_command\_list(); axi\_slave\_transaction tr; // Write command list to memory foreach(cmd\_list[i]) begin tr = axi\_slave\_transaction::type\_id::create("tr"); tr.addr = 'h3000\_0000 + i\*16; tr.data = cmd\_list[i]; tr.burst = INCR; tr.len = 3; // 4x64bit words per command start\_item(tr); finish\_item(tr); end endtask

virtual task start\_dma\_transfer(); apb\_master\_seq\_item tr; // Configure initial command pointer write\_reg(channel, 'h0C, 'h3000\_0000); // CMD\_NEXT\_ADDR write\_reg(channel, 'h40, 1); // CH\_ENABLE endtask function void initialize\_cmd\_list();

// Create scatter-gather command list cmd\_list[0] = {'h4000\_0000, 'h5000\_0000, 256, 'h0}; // CMD0 cmd\_list[1] = {'h4000\_1000, 'h5000\_8000, 256, 'h0}; // CMD1 cmd\_list[2] = {'h4000\_2000, 'h5001\_5000, 256, 'h0}; // CMD2 cmd\_list[3] = {'h4000\_3000, 'h5001\_7000, 256, 'h0}; // CMD3 cmd\_list[4] = {'h4000\_4000, 'h5002\_5000, 256, 'h3}; // Last CMD endfunction

## 4. Evaluation

## **accellera** 4. Evaluation : Evaluation Set

| Name                        | Input token     | Output token    |  |  |

|-----------------------------|-----------------|-----------------|--|--|

| openai/4o-mini              | \$0.15/M tokesn | \$0.6/M tokens  |  |  |

| anthropic/claude-3.5-sonnet | \$3/M tokens    | \$15/M tokens   |  |  |

| deepseek/deepseek-r1        | \$0.55/M tokens | \$2.19/M tokens |  |  |

TABLE II

The prices of different models used in the evaluation process

| Module Name | Code Size<br>(Lines) | Documentation<br>(Words) | Functionality Description                                          |  |  |

|-------------|----------------------|--------------------------|--------------------------------------------------------------------|--|--|

| MODULE_A    | 1706                 | 1500                     | Support address remapping for<br>multiple address ranges.          |  |  |

| MODULE_B    | 4565                 | 5500                     | Supports multi-channel DMA with<br>Register and Command list modes |  |  |

| MODULE_C    | 20495                | 21000                    | Supports protocol conversion and<br>multi-Ring management          |  |  |

|             |                      |                          |                                                                    |  |  |

TABLE III

Different DUTs (Devices Under Test) used in the evaluation process

### Evaluation Objectives

- Ensure the correctness/completeness of documents and testbench implementation, with accuracy as the core metric

- Evaluation Methods

- Compare against manual verification baseline

### Accuracy Evaluation System

- Specification Analysis: Documentation information error rate (number of errors/total volume)

- Verification Planning: TP/TC decomposition error rate (proportion of missing/incorrect items)

- Test Platform: Specification error rate (number of words requiring modification/total generated volume)

- Code Generation: Code error rate (number of lines requiring modification/total generated lines)

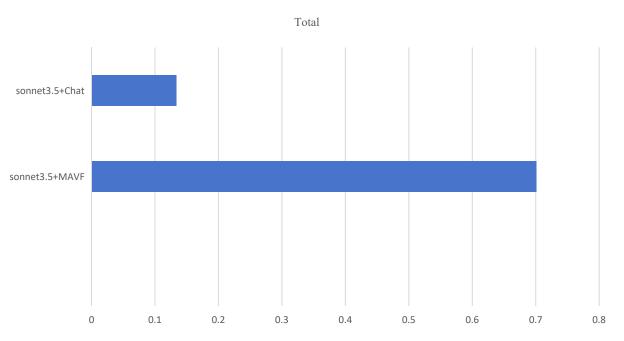

sonnet3.5+MAVF represents tests using anthropic/claude-3.5-sonnet3.5

model with full MODULE\_B design specifications as input, running

MAVF fully automatically without human intervention.

sonnet3.5+Chat represents tests using the same model in conversational

mode with full MODULE\_B design specification documents as context prompts plus specific task requirements, without human intervention.

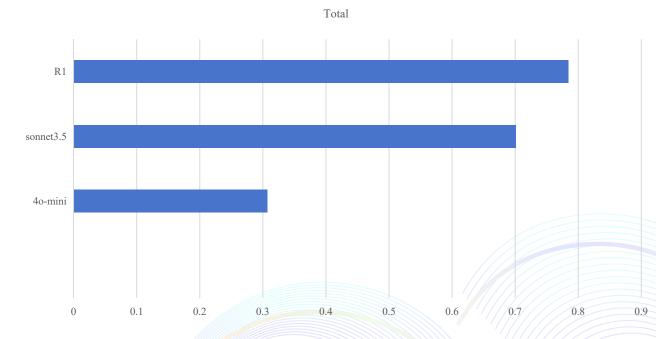

#### Figure 5. Evaluation Results of Three Different Models (Summary)

40-mini represents tests using openai/40-mini model.

r1 represents tests using deepseek/deepseek-r1 model.

Sonnet3.5 represents tests using anthropic/claude-3.5-sonnet3.5 model

All with full MODULE\_B design specifications as input and fully automated

MAVF execution without human intervention.

### 4. Evaluation: Accuracy & Efficiency

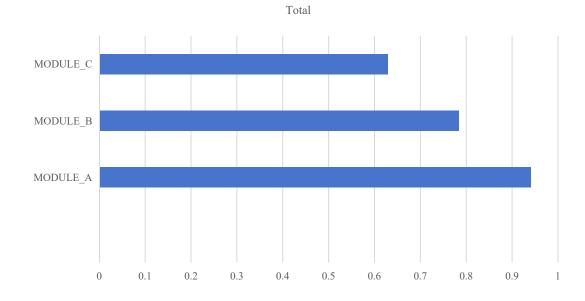

#### Figure 7. Evaluation Results of Three Different Modules (Summary)

Results show tests using deepseek/deepseek-r1 model on MODULE\_A, MODULE\_B, and MODULE\_C modules respectively, using their full design specifications with fully automated MAVF execution without human intervention.

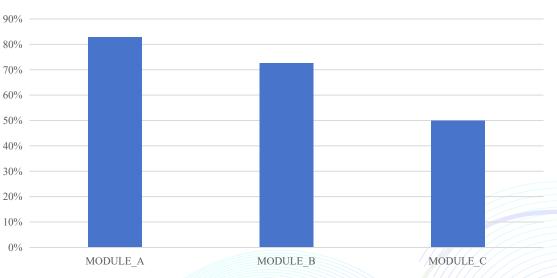

#### Time Reduction Rate

#### Figure 8. Time reduction rate (Summary)

Time reduction rate shows the percentage of time saved through MAVF assistance ((human time - human&MAVF time)/human time ×100%)

| model     | MODULE_A |        | MODULE_B |       | MODULE_C |                 |       |        |        |

|-----------|----------|--------|----------|-------|----------|-----------------|-------|--------|--------|

|           | input    | output | total    | input | output   | total           | input | output | total  |

| 4o-mini   | 378k     | 23k    | \$0.07   | 775k  | 23k      | <b>\$0.13</b>   | 878k  | 47k    | \$0.16 |

| sonnet3.5 | 402k     | 33k    | \$1.69   | 603k  | 50k      | \$2.55          | 1204k | 79k    | \$4.79 |

| r1        | 545k     | 49k    | \$0.20   | 807k  | 76k      | \$0. <b>3</b> 0 | 1080k | 111k   | \$0.84 |

Table IV

"input" shows data volume sent to models as prompts. "output" shows information volume returned by models to MAVF. "total" shows the cost calculated based on current model prices for total tokens consumed.

This demonstrates that using MAVF to assist chip verification work **offers excellent cost-effectiveness**, achieving substantial benefits **with minimal resource investment**.

## 5. Discussion

#### Innovation Value

★ Framework: Multi-agent collaboration → Solving engineering implementation problems

★ Process: Workflow decomposition → Achieving efficient GenAl integration

★ Driving IC DV into a new "AI+" paradigm

#### Framework Effectiveness

- ✓ Performance significantly better than traditional dialogue methods

- ✓ Complex design scenarios require high-performance models +

human intervention (50%+ efficiency improvement)

- Resource Efficiency

Resource costs account for <5% of efficiency gains</li>

Human input at key nodes can achieve improvements in both quality and efficiency

### Current Challenges

Lack of standardized evaluation sets

Large differences in module functionality (need to establish classification optimization system)

### Future Optimization Directions

Module feature classification: Establish template library for different designs

- Framework upgrade: Reliability/maintainability/human-computer interaction optimization

- Process optimization: Further optimize the granularity of decoupling verification process based on GenAI capabilities

- More comprehensive evaluation sets

# Q&A

### Liuwenbo\_7@foxmail.com