# System Design with Agile Verification and Continuous Acceleration

Luke Yang X-EPIC

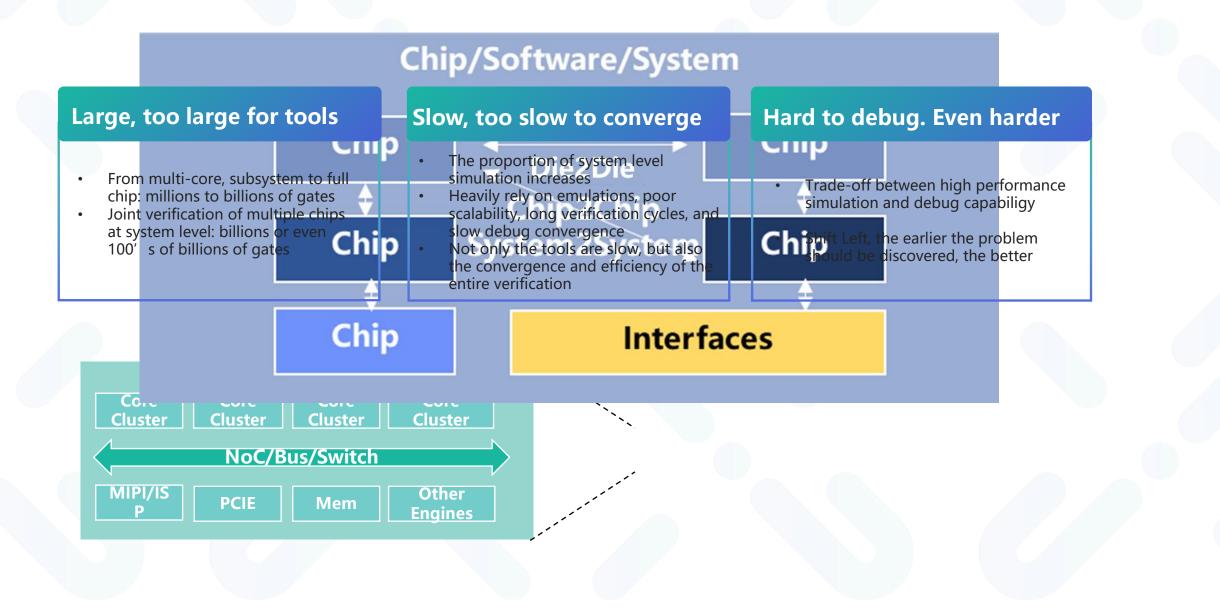

#### **Challenges in the Fast-growing System Design and Verification**

#### What do System Companies need from EDA? Faster, stronger verification systems

#### How System Companies are Re-shaping requirements for EDA

Several trend-related presentations highlighted the investments that hyperscale data center and systems companies are making in strengthening their SoC design teams in-house - e.g., Google, Meta, Microsoft, Amazon, etc.

The panel asked representatives from these companies - "What do you need from EDA?" . Their answers can be summarized as follows, "Faster, stronger verification systems."

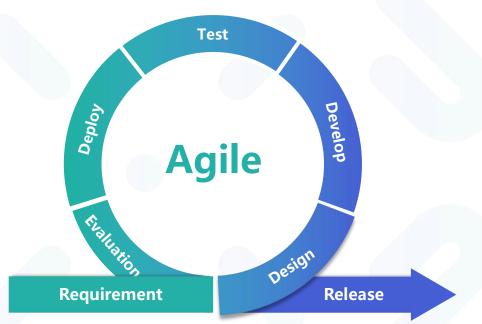

#### How can Chip Design be Agile?

#### **Software Design**

#### Chip Design

- Quick respond to changes

- Continuous testing

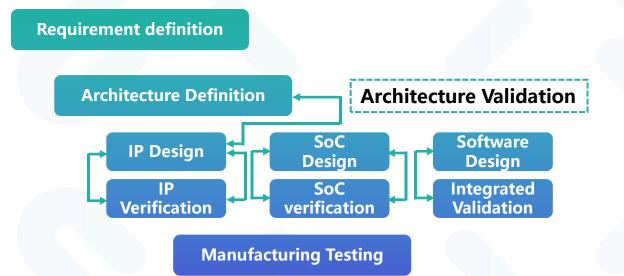

### A Long, step-after-step and highcost journey

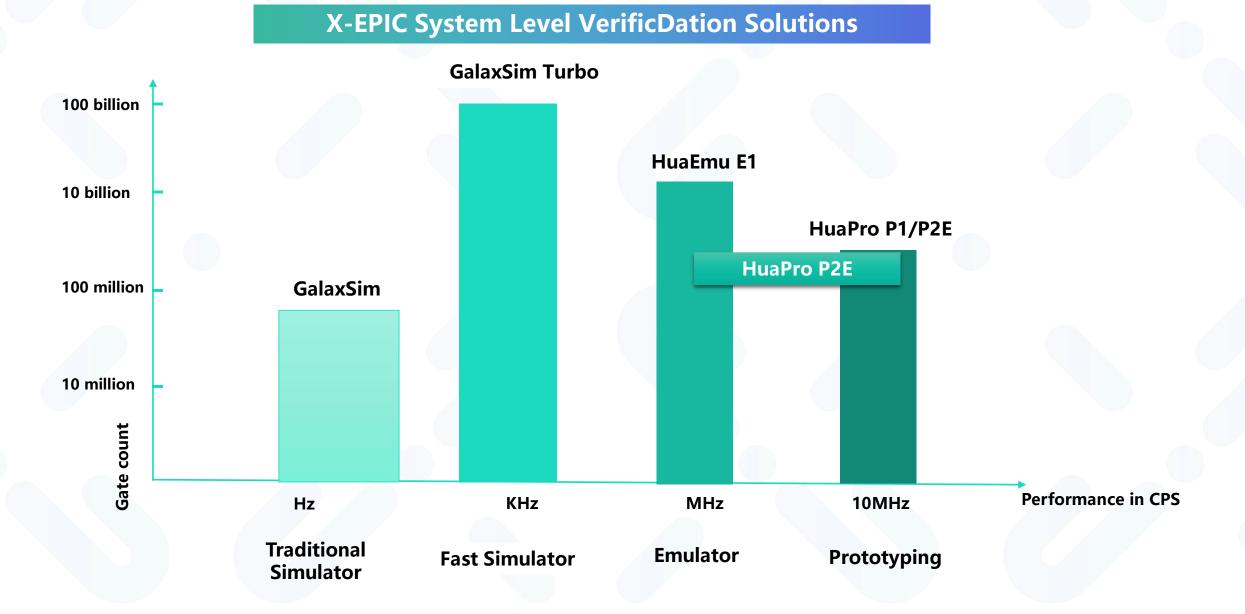

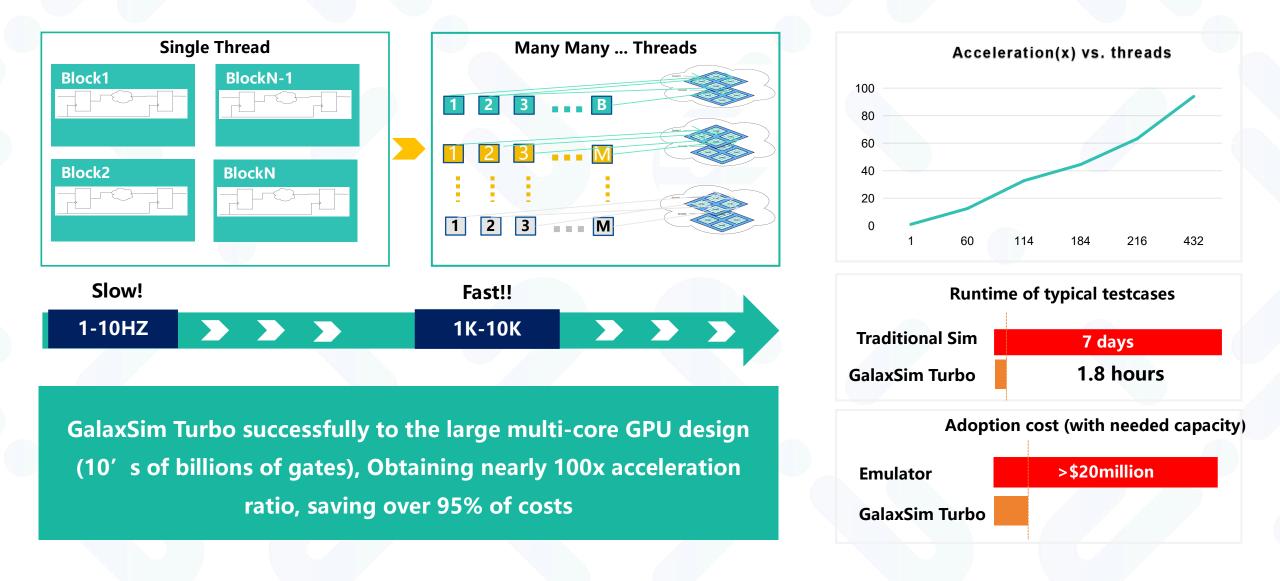

## Simulation Tools: Earlier and Continuous in Big System Design Flow X-EPIC

### System level simulation with GalaxSim Turbo for 20 billion GPU design X-EPIC

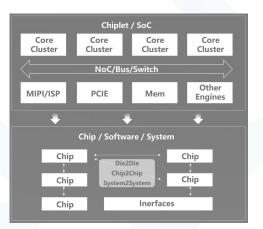

#### HuaEmu E1: Bigger Emulator for 10 Billion Level SoC to Chiplets

#### **Super Capacity**

- **Design for big designs** more than 15 billion gates design size

- High emulation memory up to 24TB in one system

- Flexible adoption from single board to multi cabinets

- Fine-grained multitask up to 128 tasks in one system

- Flexible task relocation unique symmetric architecture

- High utility rate cloud-native management system

#### **Powerful Debugging**

- **Reduce Recompilation** full vision

- Long time tracing unlimited depth dumping

- Locate the bug accurate programmable rigger

- Reproduce the bug emulation record/replay

- System Debug context save/restore

- Automatic Debug trigger calling debug command

#### **High Performance**

- **High efficiency implementation** automatic and quick compilation

- Accelerated P&R process unique symmetric architecture

- High performance dedicate optical switching protocol for low latency

- Low impact debugging high speed signal dumping

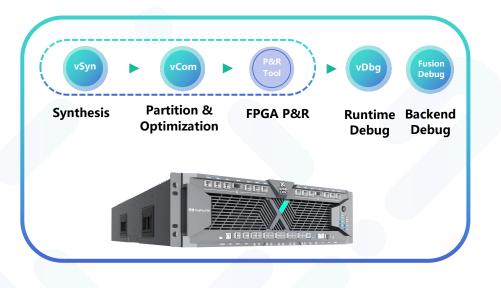

#### HuaPro P2E: Innovative Dual-mode Hardware Verification

#### Prototyping Mode

#### **Emulation Mode**

#### **Customer A – Prototyping Mode**

#### Size:

• up to 20 FPGA chips

#### **Performance:**

- 1 FPGA project 20MHz

- 20 FPGA project 10MHz

#### Prototyping flow bring up time

- Prepare FPGA version: 1 week

- vCom partition iterations: 2 weeks

- PR iterations: 2 weeks

- Performance tuning : 2 weeks

#### **Customer B - Emulation Mode**

**Performance:** 6 FPGA, 3-4MHz

Emu flow bring up time: 2.5 weeks

Solution: virtual models

Debug: Full vision, Accurate Triggers, etc.

#### **Smarter Verification: More Computing for Less Analysis**

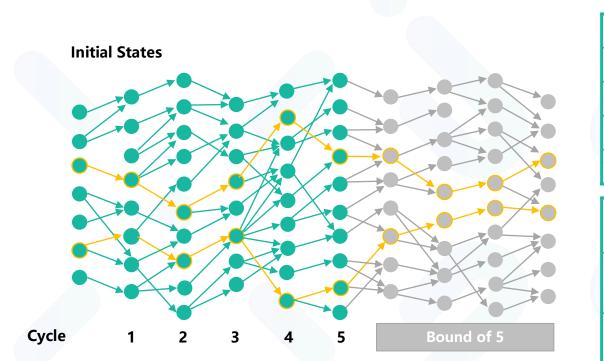

#### Simulation: enumerative method Formal: Equivalent to an exhaustive approach

Simulation: Provides stimulus comparison output

Formal: Solve for all statesMathematical solving through the solver

**Solvers**

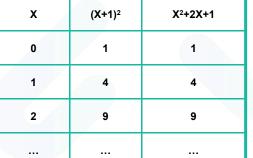

#### **GalaxFV Showing Competitive Advantage in Multiple Projects**

#### **Project 1: FIFO module in a GPGPU chip**

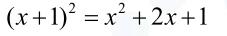

#### **Project 3:** Datapath with large data bit-width in an ADAS chip

- Addressed Challenges: Large design space, Complicated algorithm

- \* Tool A and Tool B are Main Stream FV tools

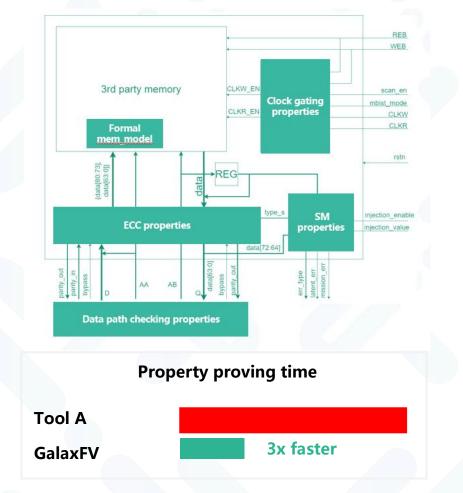

#### **Project 2:** Mem Ctrl module in an intelligent driving chip

Application Library: Mem model, error-injection model

#### How Fast Can We Do Formal UMC?

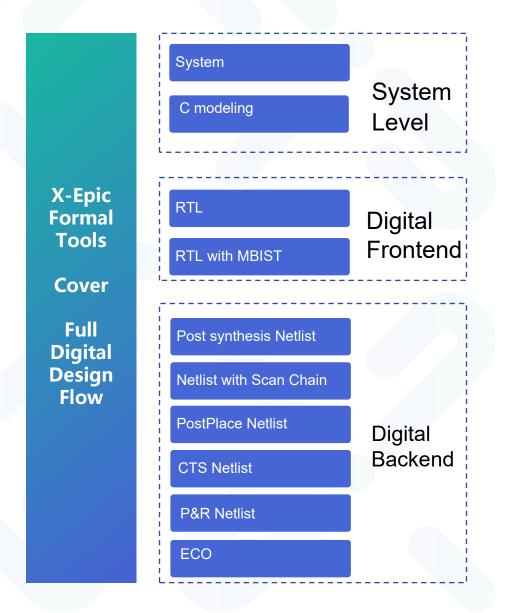

### Galax Formal: Smarter Verification Methods with Quicker Engine X-EPIC

HEC **High Level Equivalence Checking**

C/C++ model VS RTL checking, often used in data path algorithm design flow

#### **Model Checking Model Properties Proving**

Static formal proving based on properties, for complete design function verification

SEC **Sequential Equivalence Checking**

Exhaustive equivalency checking for circuits with state transitions and outputs

#### LEC Logic Equivalence Checking

Check different representations of a combinational circuit are functionally equivalent

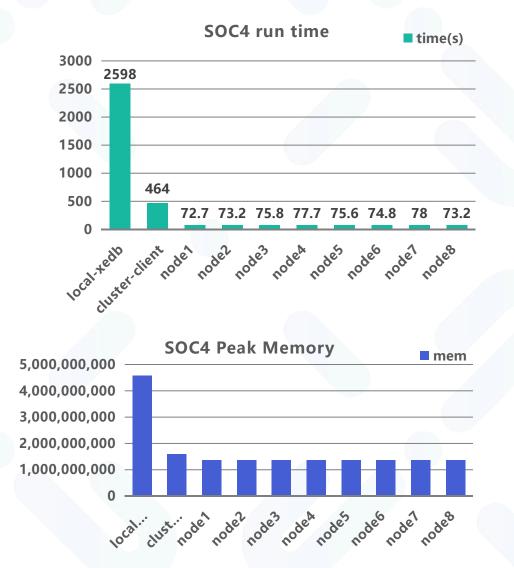

#### **XEDB: Quicker Database to Improve Efficiency**

**5**X

| Case Name Nu |              | Number of signals |           | Number of vc   |

|--------------|--------------|-------------------|-----------|----------------|

| SOC4         |              | 10million         |           | 10,000 million |

|              |              |                   |           |                |

| Case Name    |              |                   | Run time  | Memory         |

| SOC4         | local xedb   |                   | 43m18.476 | s 3.95G        |

|              | cluster-xedb |                   | 7m44.946s | 1.59G          |

|              | xedb-node    |                   | 72s ~ 78s | 1.35G          |

Prove distributed XEDB write times compared to XEDB Reduced by more than

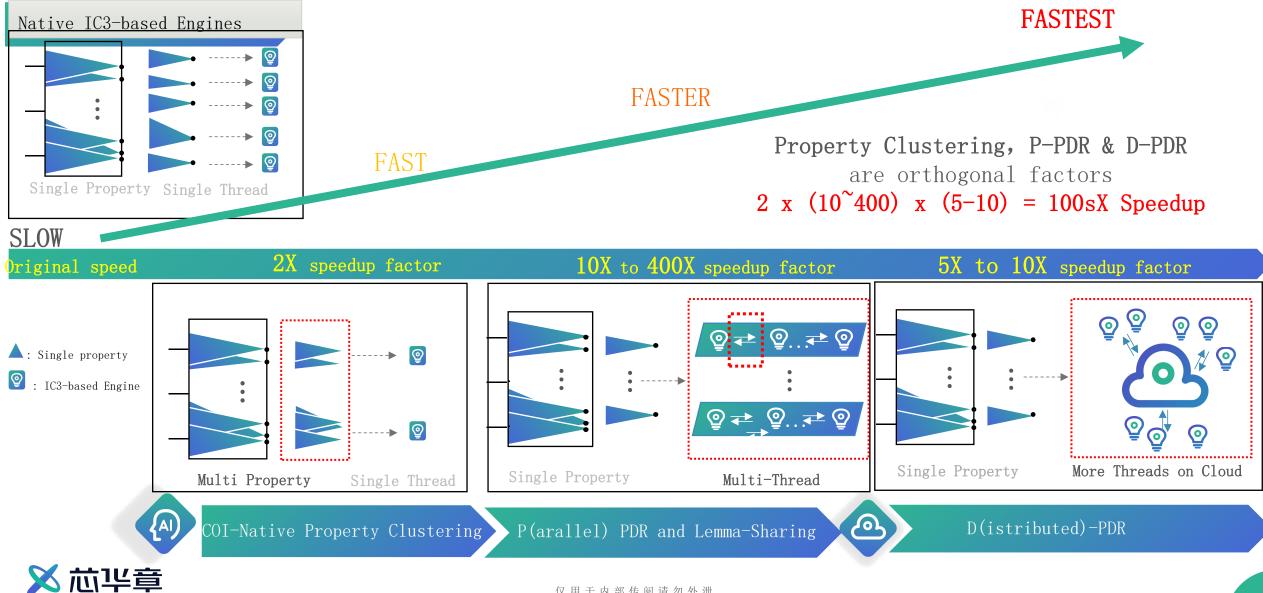

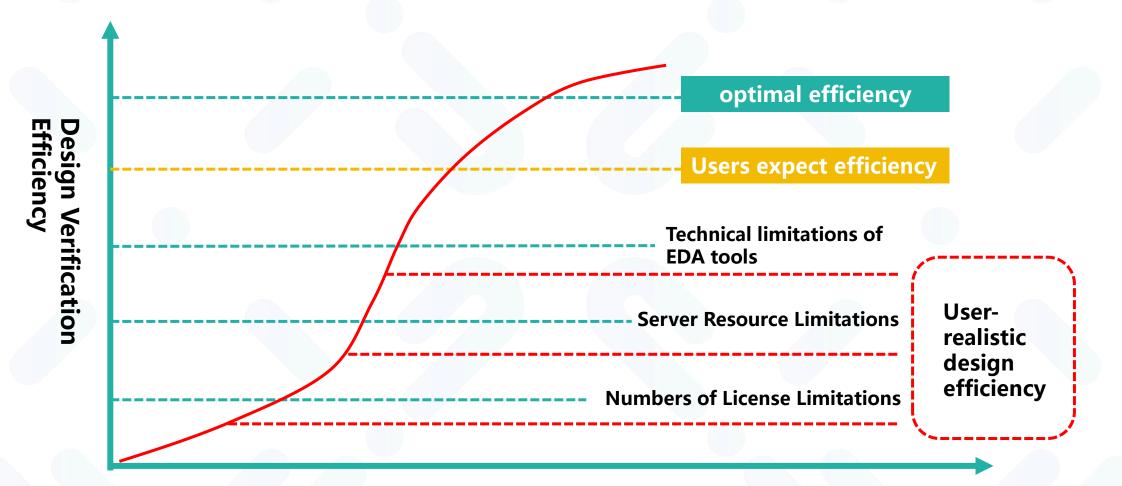

#### **Cloud Native EDA: Unlimited Computing for 100x Accelerating**

**Computational parallelism and automation of EDA**

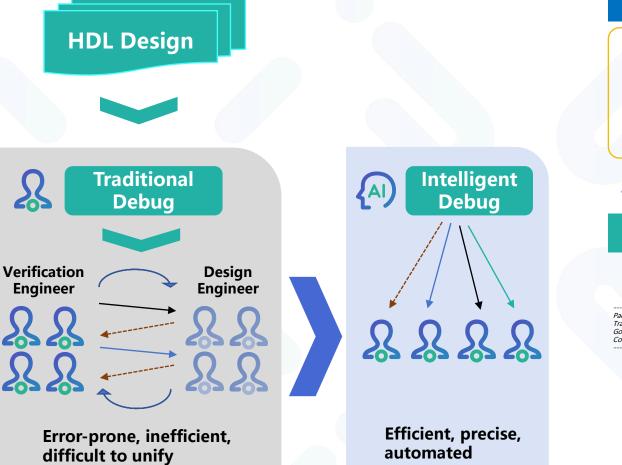

#### **Debugging with Data Driven methods**

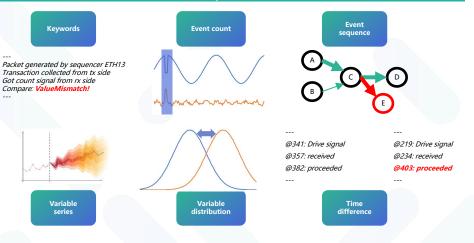

#### Use NLP to improve adaptability

#### **User prompt**

- a. UVM\_INFO ...@...: data transmitted via Ethernet

- b. UVM\_INFO ...@...: data sent by Ethernet

Q: Are they from the same log event?

**)** Yes, they are the same event

#### Rich failure-type mining models

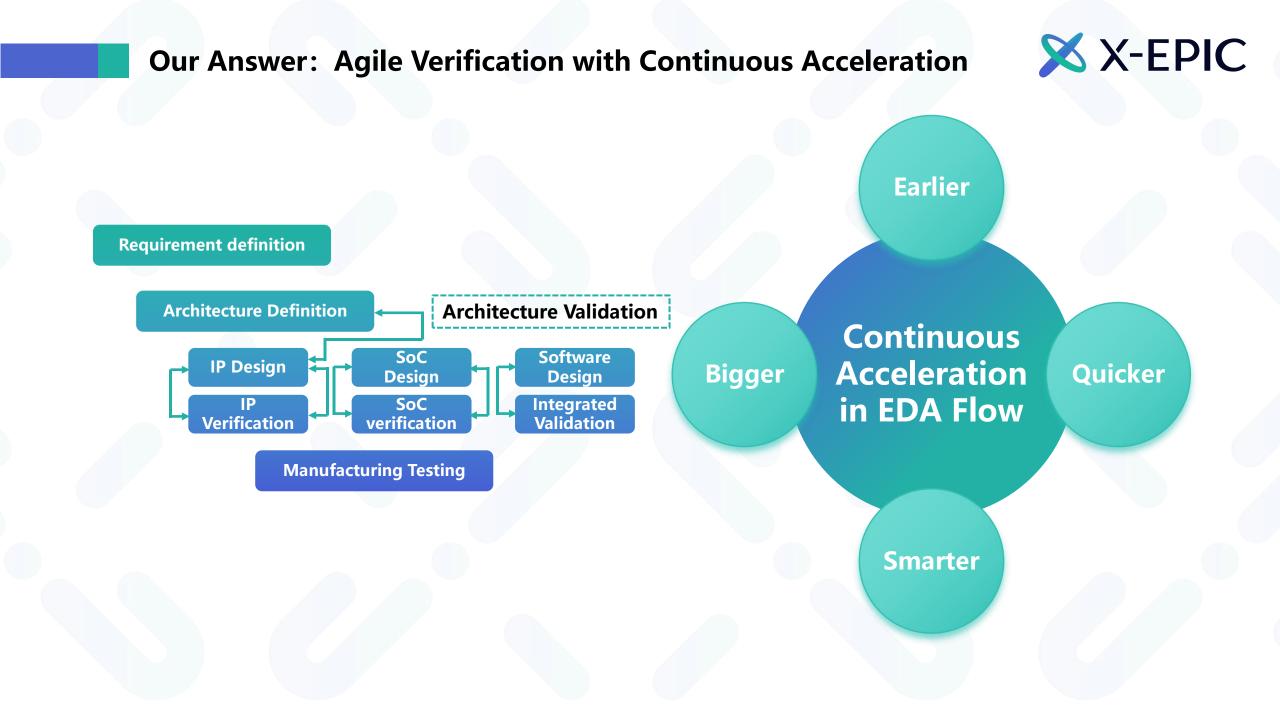

#### **XEPIC** provides platform and tools for Agile Design Verification

**Continuous Acceleration for Agile System Verification**

#### **Unified EDA database**

**Fusion Debug**

**Unified Debug Tool for Large System Verification**

HuaPro P1/P2E

Dual Mode Hardware Assisted Verification

GalaxSim Turbo

**System Level Simulation**

HuaEmu E1

Hardware Emulation System GalaxFV/EC

**Formal Verification**

GalaxPSS

**Smart Scenario Stimulus**

## X-EPIC Accelerating System Verification