## **AI-Driven Verification**

Leveraging AI to Achieve the Next Leap in Productivity

Yogesh Goel VP Product Engineering, Systems and Verification Group

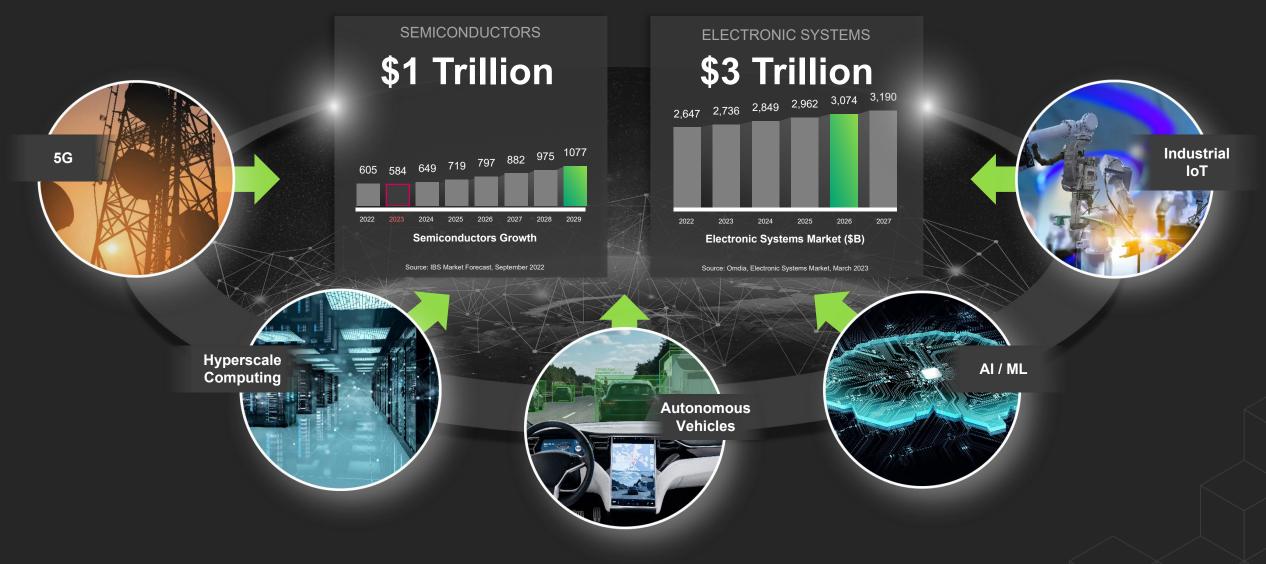

#### Five Generational Trends, All Anchored Around Compute

#### Productivity Challenge in Chip and System Design

Complexity Is Increasing

Source: Cadence analysis

More Annual Design Starts

**4X**

Over the Next Decade

(<=10nm)

Source: IBS Global Semiconductor Industry Service Report: Design Activities and Strategic Implications, July 2022 Source: Cadence analysis

#### Not Enough Engineers

**Semiconductor Engineering**

**Engineering Talent Shortage Now Top Risk Factor**

FEBRUARY 25TH, 2019 - BY: MARK LAPEDUS

Source: https://semiengineering.com/engineering-talent-shortage-now-top-risk-factor/

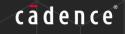

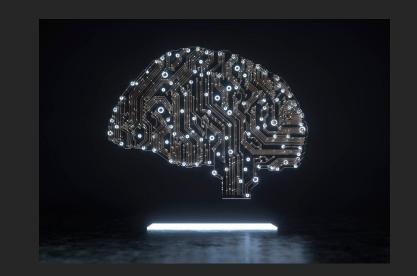

## AI – Accelerating System Design Productivity

## Power of the Human

Human engineer: solve complex problems and be creative

cadence

- Design algorithms

- Innovate new architectures

- Think outside the box

#### Data Volume

## Power of AI Algorithms

Human limitation: serial data processing

Al strength: insights from parallel processing big data

cadence

- Chat bots

- Speech from text

- Image from text

- Recommending ads

• ...

Data Volume

Power of AI-Driven Solutions Accelerate the human in the loop

#### Data Volume

## Human in the Loop AI Solutions – Pilot & Co-Pilot

"...rather than thinking about a competition between humans and machines, we should find a way in which the two work together"

Terwiesch & Ulrich – wsj.com

World Business U.S. Politics Economy Tech Finance Opinion Arts & Culture Lifestyle Real Estate

THE WALL STREET JOURNAL.

TECHNOLOGY ARTIFICIAL INTELLIGENCE

#### M.B.A. Students vs. ChatGPT: Who Comes Up With More Innovative Ideas?

We put humans and AI to the test. The results weren't even close.

Challenge – Generate 200 "New Business" ideas : AI (ChatGPT) - ~1h; Humans (Wharton MBA Students) – Days

Human in the loop AI – Pilot & Co-Pilot Human (Pilot) – Identify the problem. AI (Co-pilot) – Report what is known about the problem. Human + AI – Iterate on unique and creative solutions to the problem.

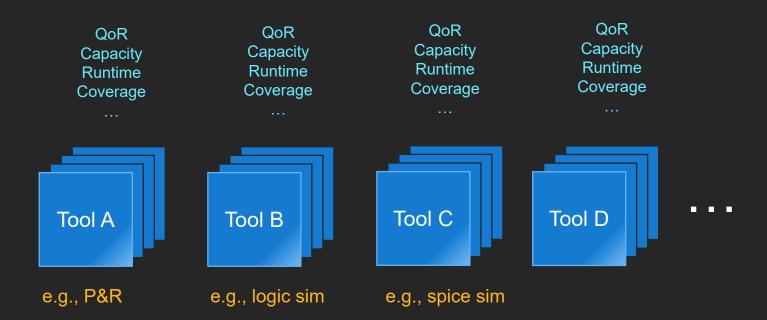

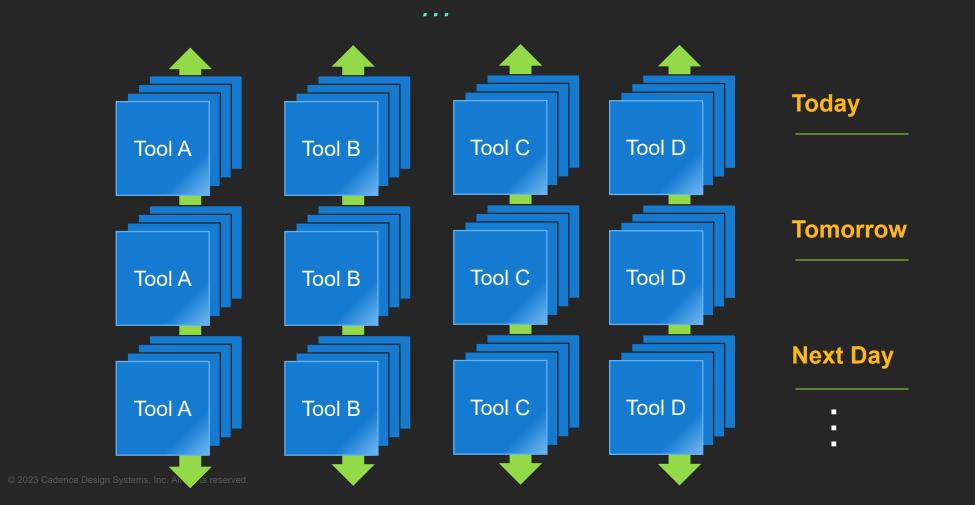

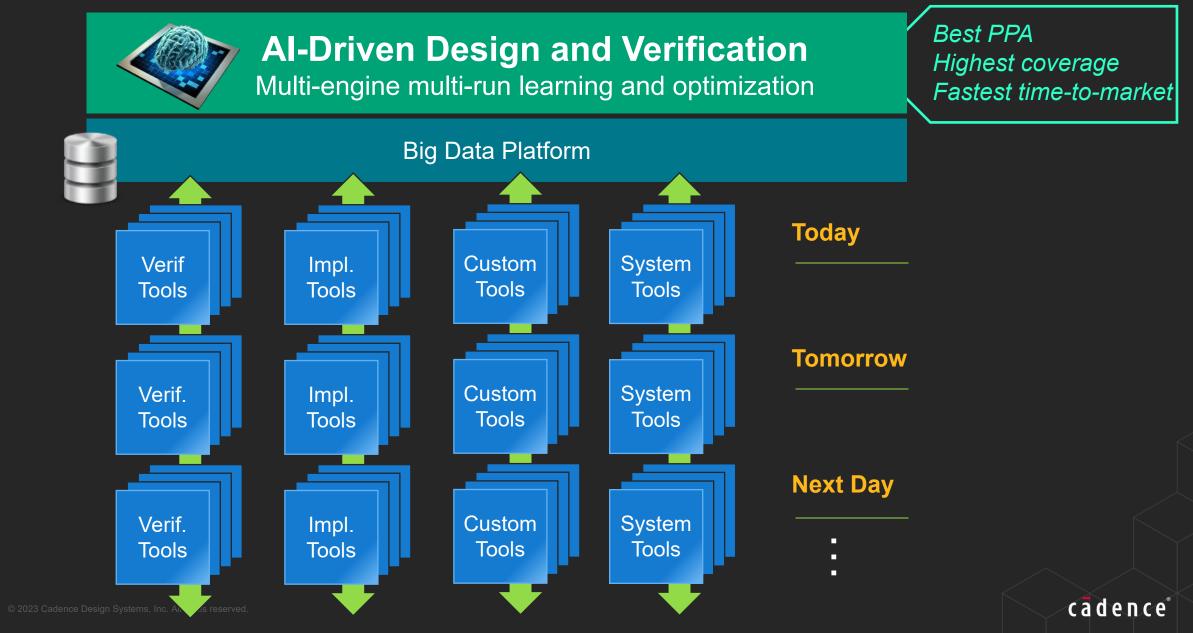

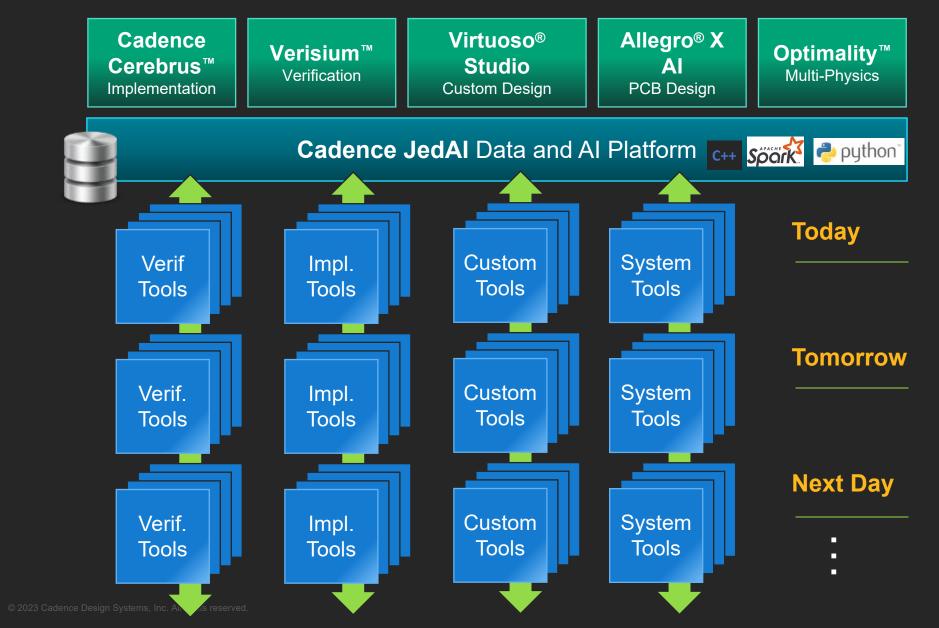

#### Traditional EDA

#### Meet PPA Goals Meet Coverage Goals

#### Next Generation Al-Driven EDA

## Cadence AI-Driven Transformation

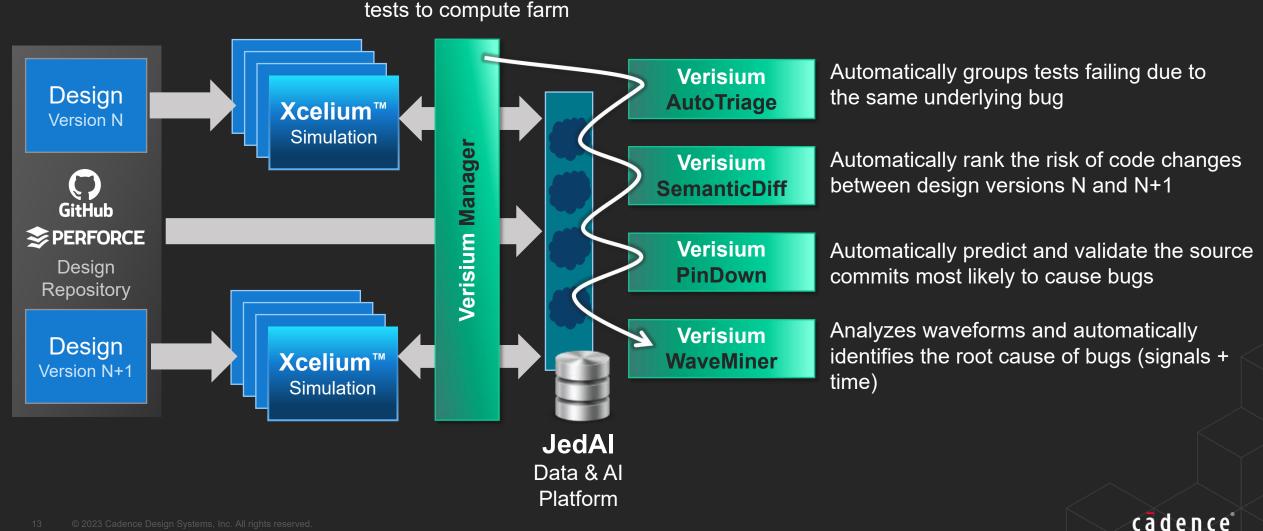

#### **Next-Generation AI-Driven Verification Workflow** Cadence Verisium<sup>™</sup>

Al-driven submission of

## Al Driven Workflow: 3x – 60x Productivity Gain Verisium<sup>™</sup> Results

| <b>30X</b>                             | <b>3.3X</b>                        | 6X                                    |

|----------------------------------------|------------------------------------|---------------------------------------|

| <b>Faster Waveform Analysis</b>        | Reduction Failure Triage Time      | Total Debug Effort Improvement        |

| Memory Controller IP                   | Block and System-Level Regressions | Automotive SoC                        |

| <b>60X</b>                             | <b>10X</b>                         | <b>4X</b>                             |

| Less Effort for Design Change Analysis | Productivity End to End SoC Debug  | Faster Identification of Buggy Source |

| >1B Gate Mobile SoC                    | Mobile SoC                         | Interface IP                          |

| <b>4X</b>                              | <b>20X</b>                         | <b>BX</b>                             |

| Better TaT for Bug Fixes               | Faster Verification of Changed RTL | Regression CPU Time Reduction         |

| CPU Core IP                            | RISC-V CPU                         | Image Sensor IC                       |

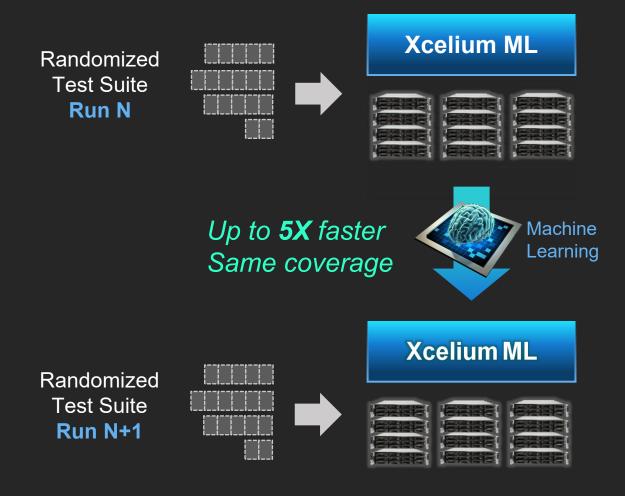

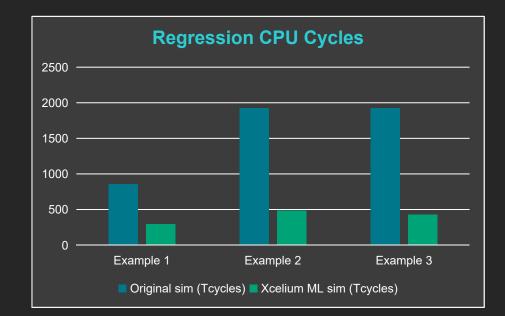

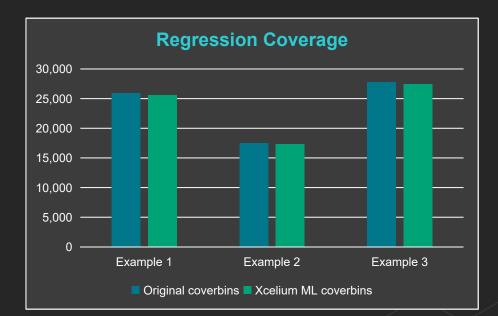

#### Al-Driven Simulation Performance Cadence Xcelium™ ML

#### Al-Driven Formal Proof Cadence Jasper<sup>™</sup> Proof Master

**Jasper Proof Master AI-Driven Formal Proof** Proof Profiling **Proof Caching Proof Orchestration** Data • Keep engine-level • Reuse the existing Use Machine settings that result if the Learning to find the worked before constraints and best proof algorithm COI are unchanged settings **Multi-run optimization** +AI

| Testcase | Baseline | Smart Proof | Gain |

|----------|----------|-------------|------|

| Α        | 50%      | 59%         | 1.2X |

| В        | 69%      | 69%         | 1.0X |

| С        | 12%      | 25%         | 2.1X |

| D        | 44%      | 83%         | 1.9X |

| E        | 57%      | 94%         | 1.6X |

| F        | 68%      | 69%         | 1.0X |

| Total    | 53%      | 71%         | 1.3X |

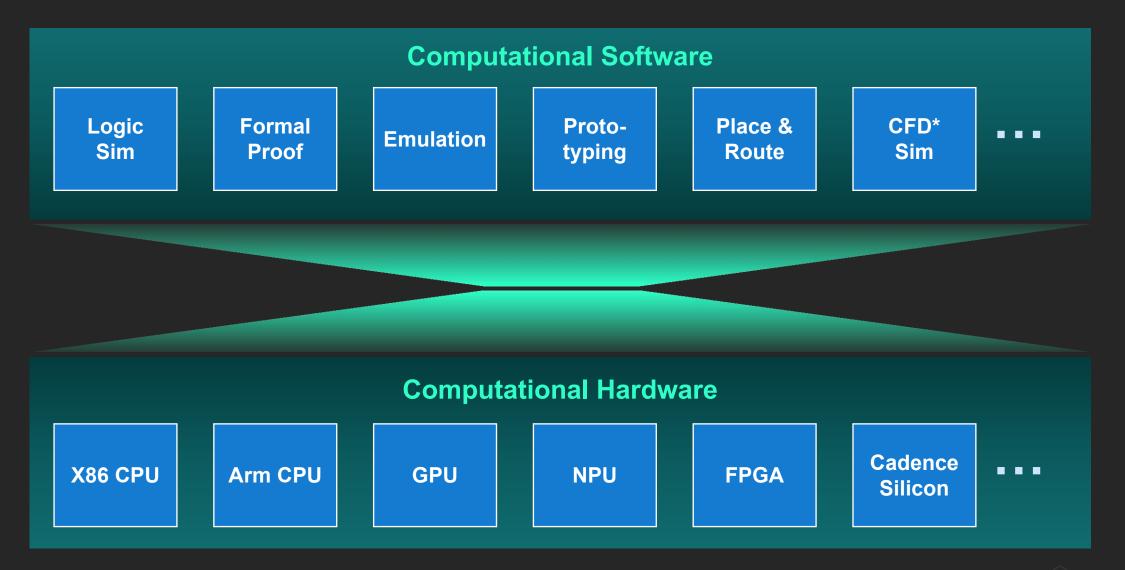

## Domain-Specific Compute in EDA

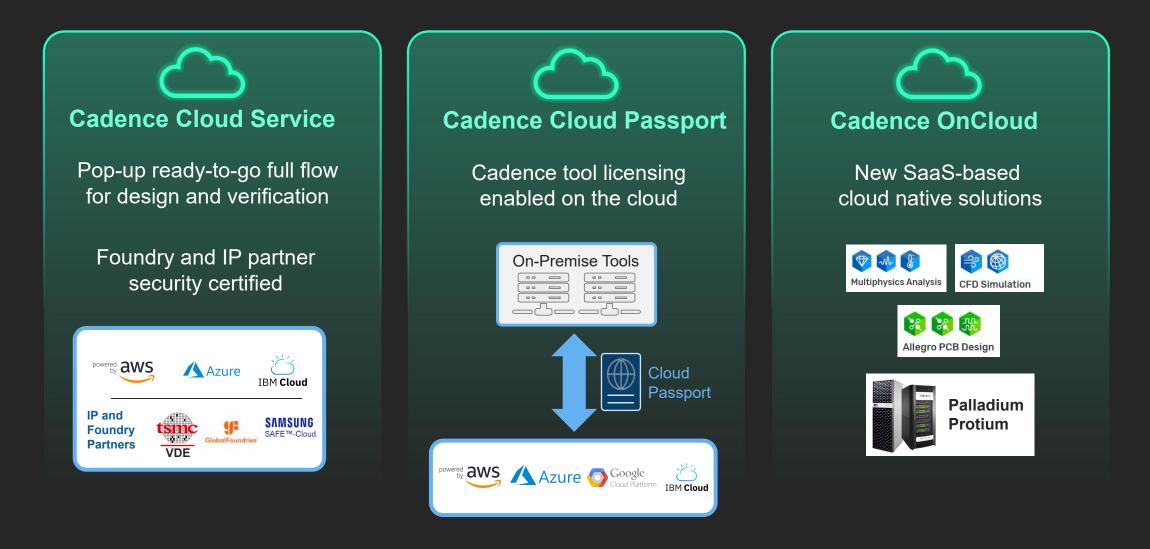

#### Domain-Specific Compute for EDA on the Cloud

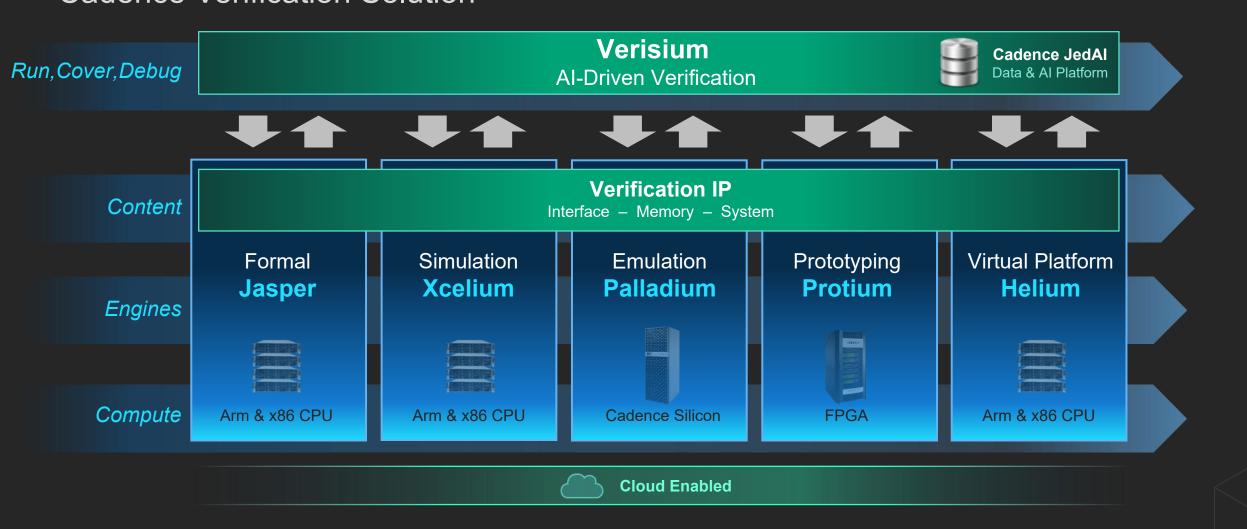

#### Next-Generation AI-Driven Verification Full Flow Cadence Verification Solution

# cadence®

© 2023 Cadence Design Systems, Inc. All rights reserved worldwide. Cadence, the Cadence logo, and the other Cadence marks found at <u>www.cadence.com/go/trademarks</u> are trademarks or registered trademarks of Cadence Design Systems, Inc. Accellera and SystemC are trademarks of Accellera Systems Initiative Inc. All Arm products are registered trademarks or trademarks of Arm Limited (or its subsidiaries) in the US and/or elsewhere. All MIPI specifications are registered trademarks or trademarks or service marks owned by MIPI Alliance. All PCI-SIG specifications are registered trademarks or trademarks of PCI-SIG. All other trademarks are the property of their respective owners.