## Agenda

### Introduction

- Synopsys Hybrid Technologies

- Use-cases and Successes

- Synopsys Hybrid Innovation

- Conclusion

- Q&A

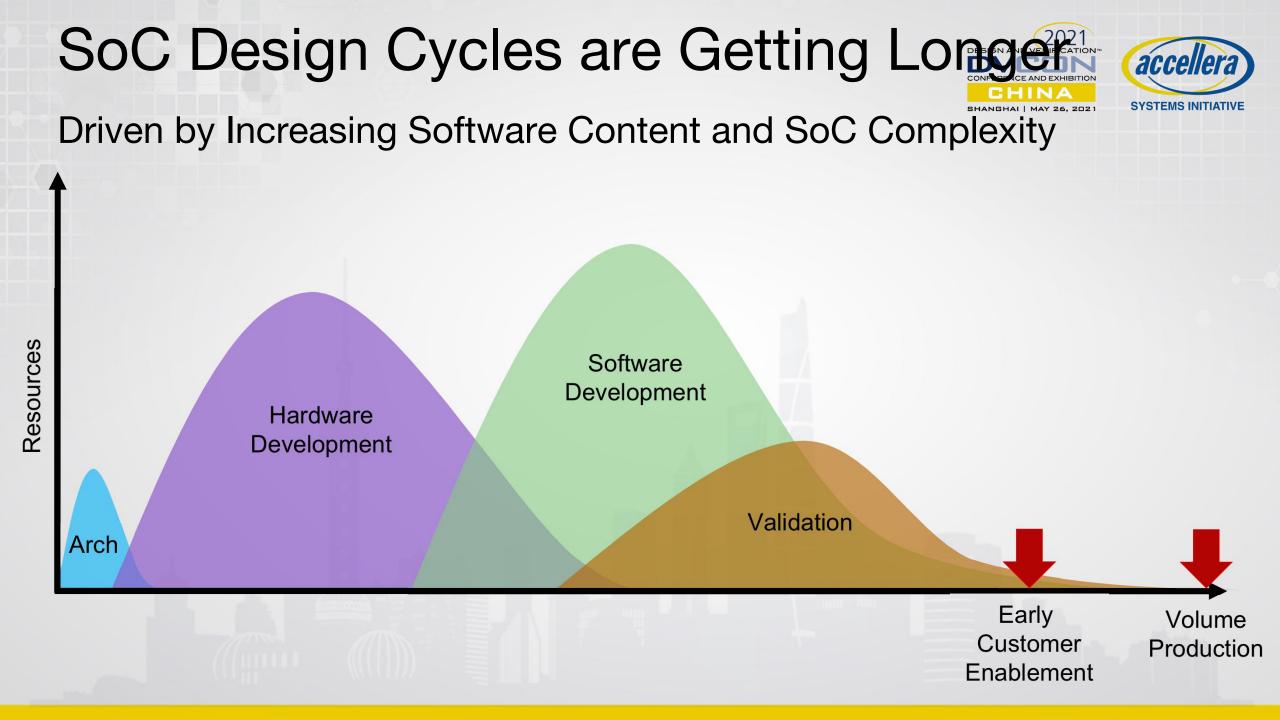

# How to Verify HW/SW Systems Faster?

alidation

Virtual Prototyping Have we exercised real-RTL?

Emulation Is the speed good enough for SW Development ?

FPGA Prototyping Do I have Prototype-ready RTL and Capacity?

How about a Hybrid ? Combining best of all the three for Faster to SW

Faster Time

Software Faster Enablement for SW Development

Arch

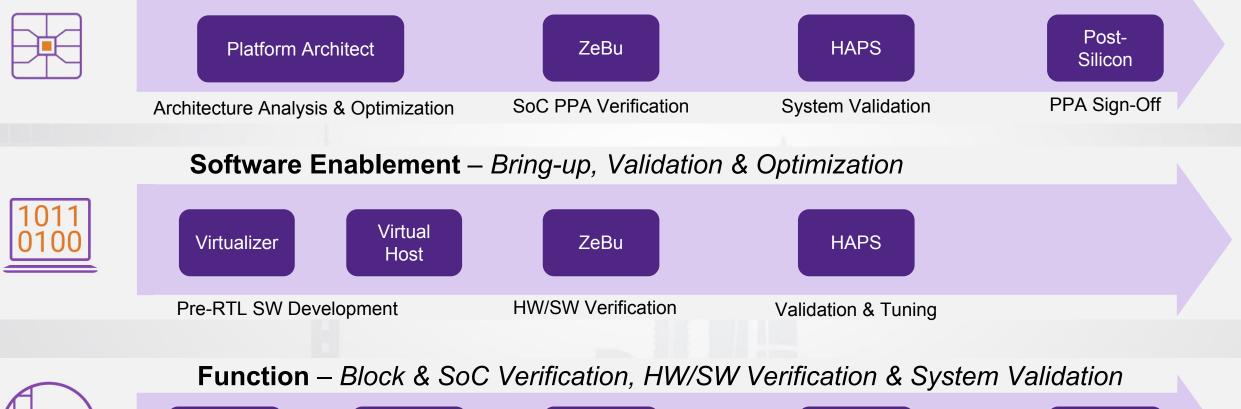

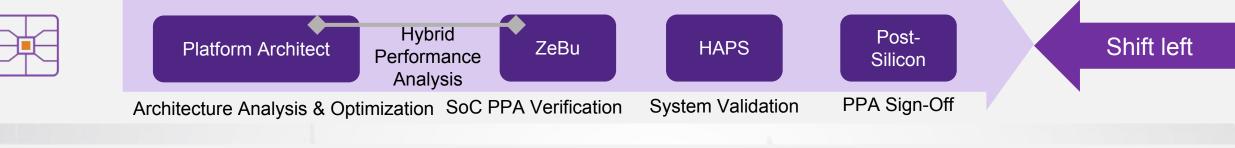

# **SoC Verification Flow**

**Performance & Power** – Architecture Analysis, Optimization & Verification

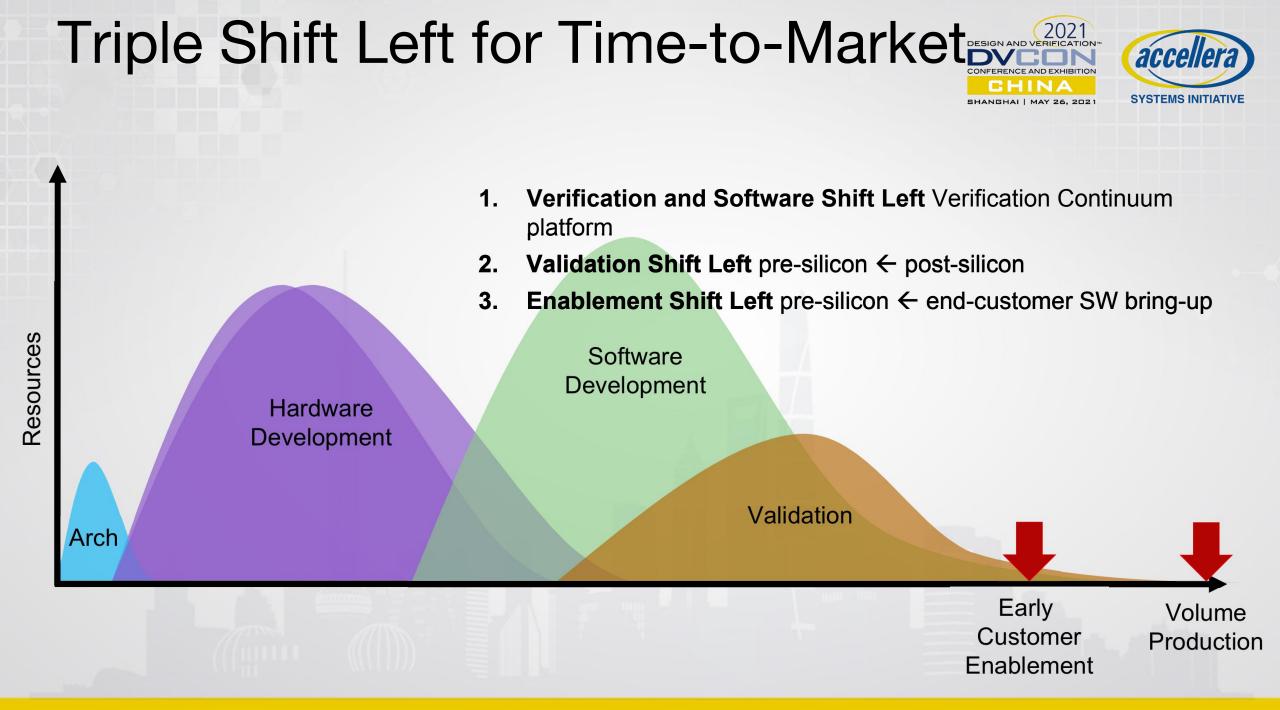

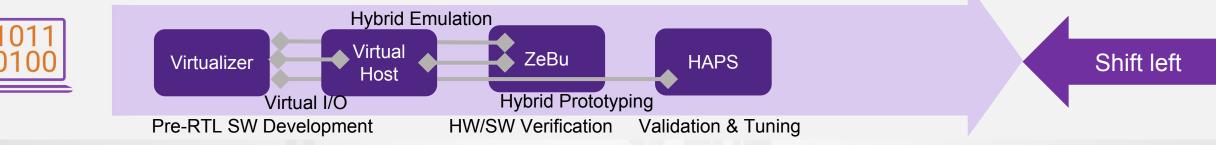

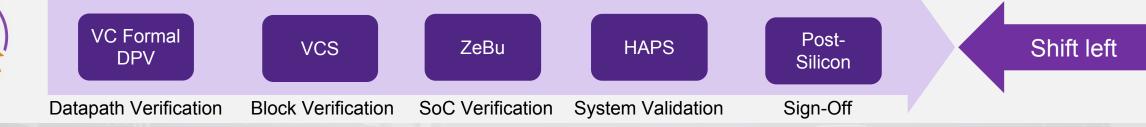

# Shift-left with Synopsys Hybrid Solution

### **Performance & Power** – Architecture Analysis, Optimization & Verification

### **Software Enablement** – Bring-up, Validation & Optimization

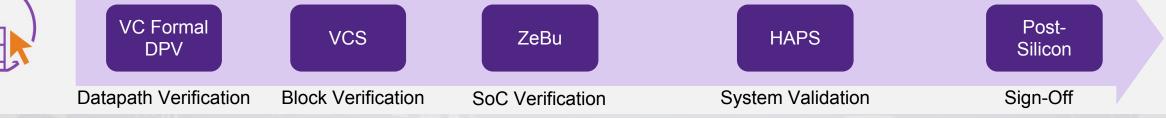

### **Function** – Block & SoC Verification, HW/SW Verification & System Validation

# **Synopsys Hybrid Solution**

- Hybrid Architecture Analysis

- Efficient architecture analysis and smart performance monitoring

- Offline and online analysis of performance data collected on ZeBu

- Faster PPA optimization, helping shift left verification cycle

- Hybrid Emulation

- Early Driver/Firmware/Application development

- Complete SoC model using VDK and synthesizable RTL IPs

- Power and performance validation over billions of application cycles

- Hybrid Prototyping

- Software driven system validation with real-world IO

- Early Driver/Firmware/Application development

- Modular and scalable validation from IP to system level

ZeBu

#### Software Driven Verification Project Flow accelle SYSTEMS INITIATIVE SHANGHAI | MAY 26, 2021 Production Software Stack $\rightarrow$ SW Signoff before Tapeout Hybrid Emulation SW Driven CPU Model + IP/SoC RTL SoC RTL **Full System Validation** ZeBu ZeBu VDK SoC Hybrid TLM Model 10 MHz 1+MHz SW Development VDK CPU Model + IP/SubSys RTL Platform SoC RTL 10~100+MHz HAPS HAPS VDK Hybrid 20**- MH**z SW Driven 10~200M **IP/Subsystem Validation**

Hybrid Prototyping

Continuous SW Driven Development/Verification Platforms

### Agenda

- Introduction

- Synopsys Hybrid Technologies

- Use-cases and Successes

- Synopsys Hybrid Innovation

- Conclusion

- Q&A

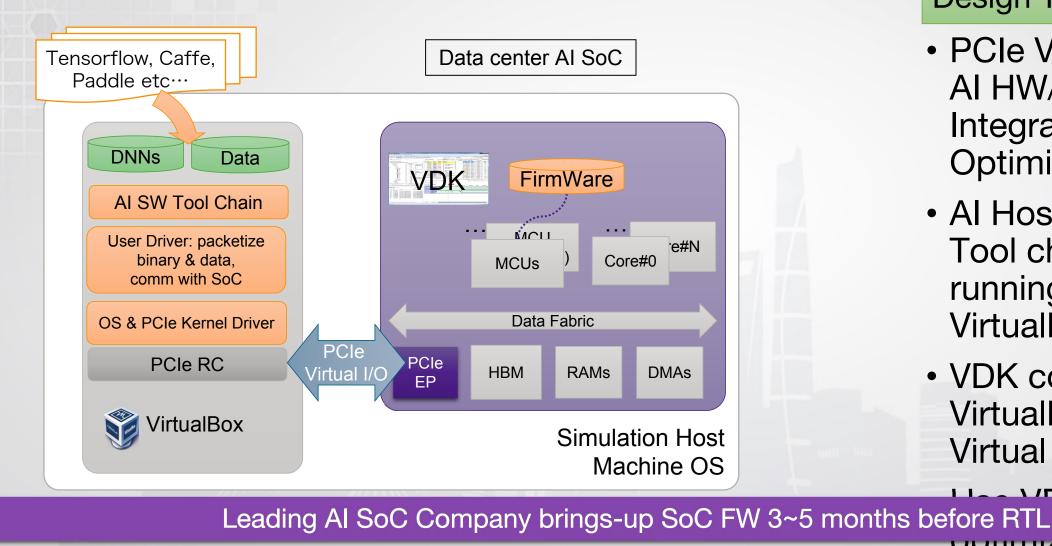

# Using VDK to Bring up AI SoC FirmWare

### Design Type : AI SoC

- PCIe Virtual I/O for AI HW/SW Integration & Optimization

- AI Host OS and SW Tool chain SW running on VirtualBox

- VDK connected to VirtualBox via PCIe Virtual I/O

Uptimize OVV TOOL

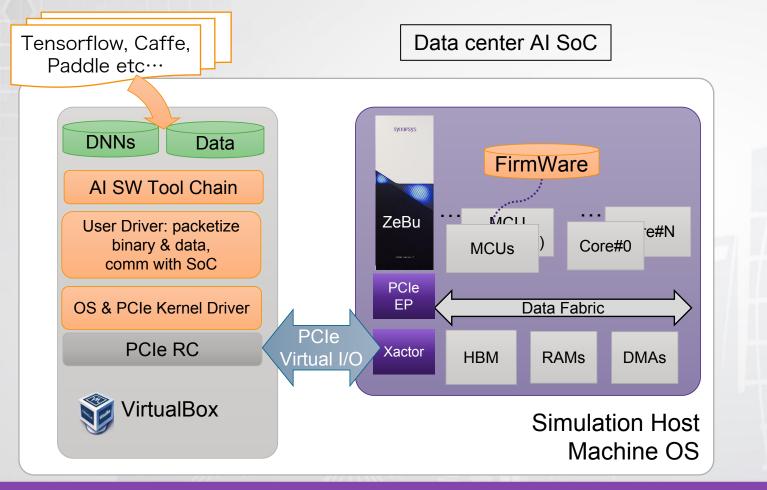

# **Use Case: Virtual Host**

### Reuse VirtualBox setup for ZeBu HW/SW validation

### Design Type : AI SoC

- Same VirtualBox setup

- Speed up HW/SW validation and turning performance

- Re-use mature host side AI SW tool chain, driver, and SoC Firmware develo

based on VDk

published in SNPS WeChat

Smooth Transition to Emulation for Validation

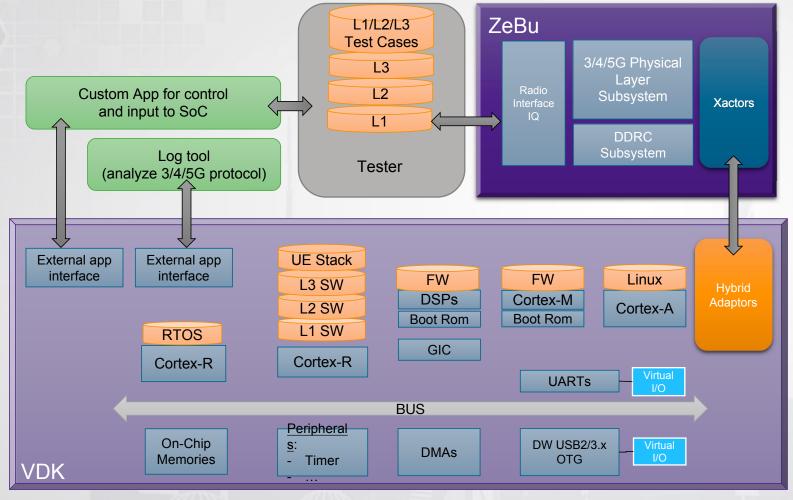

# **Use Case: Hybrid Emulation**

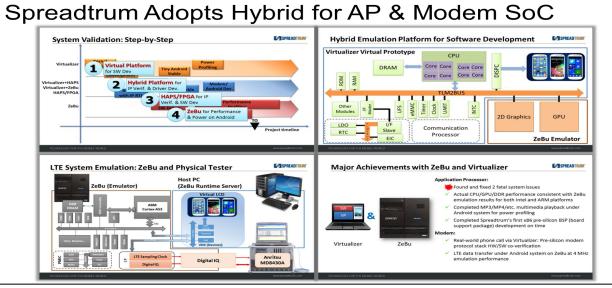

### 5G Modem Full HW/SW Verification Platform

### Design Type : 5G Modem

- Start full-stack 5G HW-SW co-verification and testing 6~9 months earlier

- OS boot within 10 minutes - run one 5G case in 15 min

- Users identified more than 100 HW/SW issues on hybrid platform before tape out

- More productive HW/SW

Leading Networking Company Starts Full-stack 5G Co-verification 6-9 months earlier

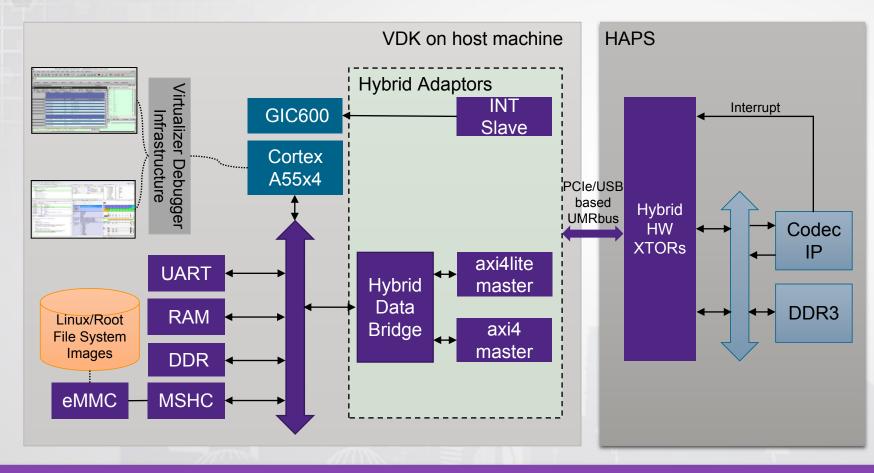

# Use Case: Hybrid Prototyping

Accelerating SW Development and RTL Validation

### Design Type : Drone SoC

- Easy Setup

- VDK with custom OS

- Different IPs in HAPS

- Smaller prototype

- Faster prototype compile

- Debug Productivity

- Boots OS in <1 minute

- OS trace/profiling helps HW/SW debug and SW performance analysis

- Full HW debug visibility for registers/pins

- Fast Speed

4K 100 Frames Encoding took 3mins to complete in hybrid, while in pure FPGA it

Leading Asia Drone Company boots Linux in <1 minute

# **Customer Successes**

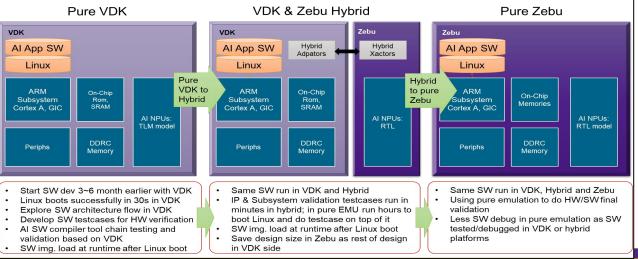

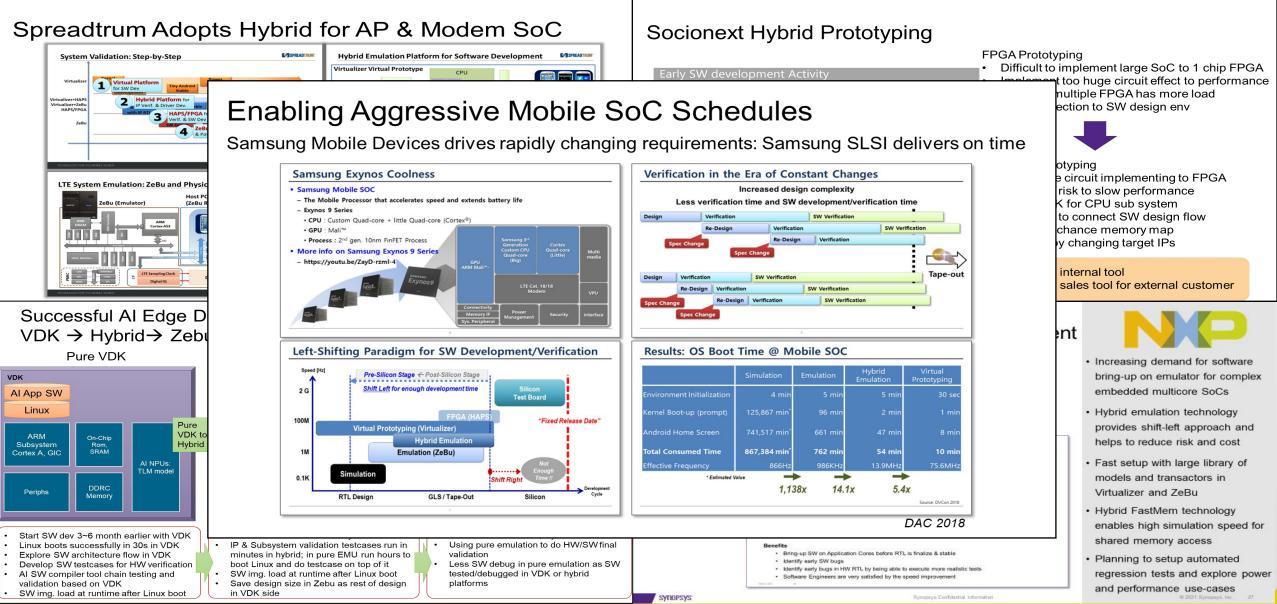

### Successful AI Edge Design Case: A Leading AI System Company VDK $\rightarrow$ Hybrid $\rightarrow$ Zebu Smooth Design/Verification Flow

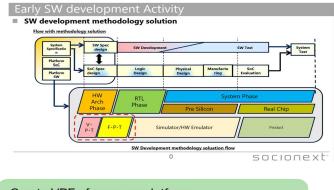

### Socionext Hybrid Prototyping

#### Create VPF of common platform

- Good usability

- Early start of OS porting/basic SW development

#### **FPGA** Prototyping

- Difficult to implement large SoC to 1 chip FPGA

- Implement too huge circuit effect to performance

- Divide to multiple FPGA has more load

- Smooth connection to SW design env

#### Hybrid Prototyping

- Minimize circuit implementing to FPGA

- Reduce risk to slow performance

- Use VDK for CPU sub system

- Flexible to connect SW design flow

- Easy to chance memory map

- Reuse by changing target IPs

#### Use as internal tool

Use as sales tool for external customer

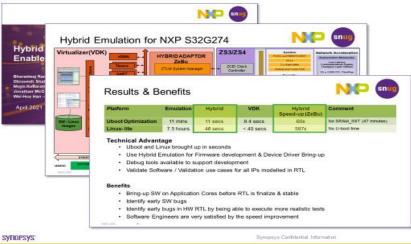

#### Hybrid Emulation for faster SW development

Presented by NXP and Synopsys at SNUG World 2021

- Increasing demand for software bring-up on emulator for complex embedded multicore SoCs

- Hybrid emulation technology provides shift-left approach and helps to reduce risk and cost

- Fast setup with large library of models and transactors in Virtualizer and ZeBu

- Hybrid FastMem technology enables high simulation speed for shared memory access

- Planning to setup automated regression tests and explore power and performance use-cases

2021 Symposy. Inc. 27

# **Customer Successes**

## Agenda

- Introduction

- Synopsys Hybrid Technologies

- Use-cases and Successes

- Synopsys Hybrid Innovation

- Conclusion

- Q&A

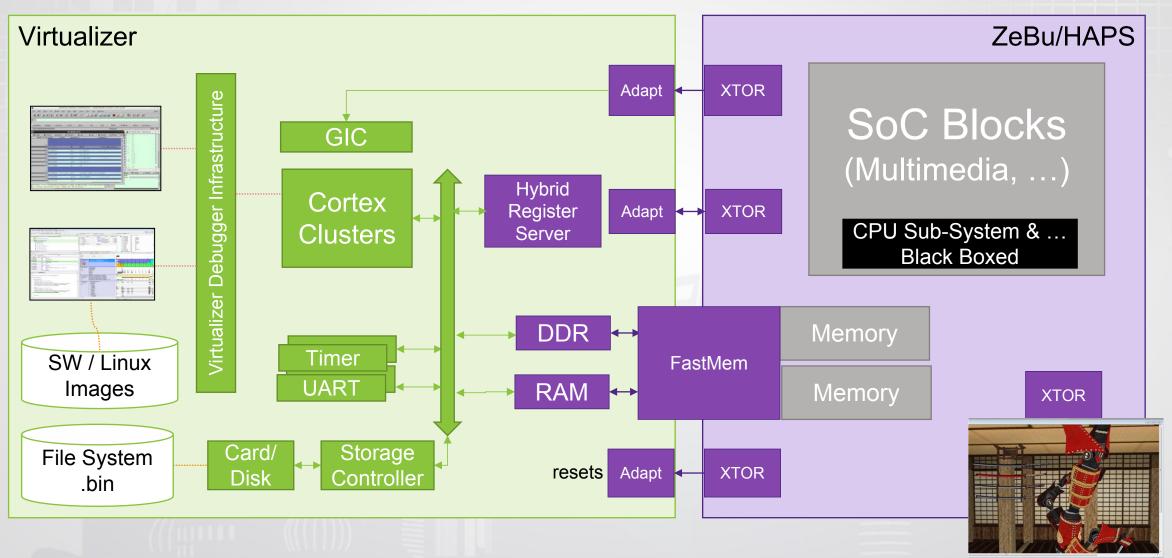

# Typical Hybrid Block Diagram Overvie

SHANGHAL | MAY 26, 2021

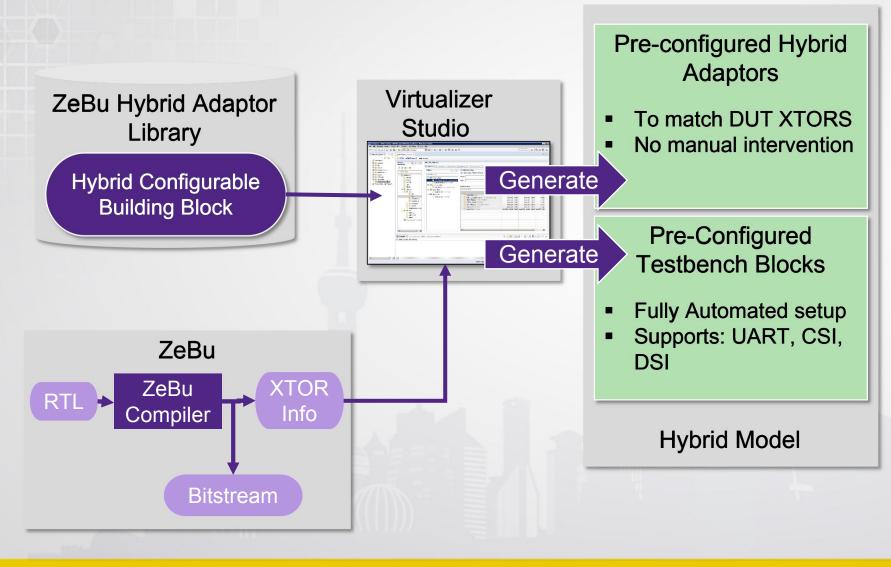

# **10x Faster Hybrid Creation**

**Configurable Hybrid Building Block**

- 10x faster Hybrid setup

- Fully Automated

- Correct by construction

- Pre-configured ZeBu Testbenches for UART/CSI/DSI

- Automatically generate templates for Custom monitors and testbenches

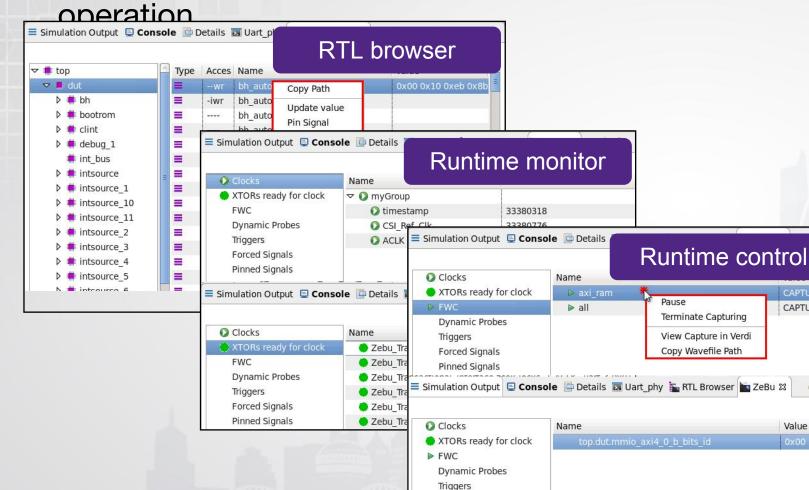

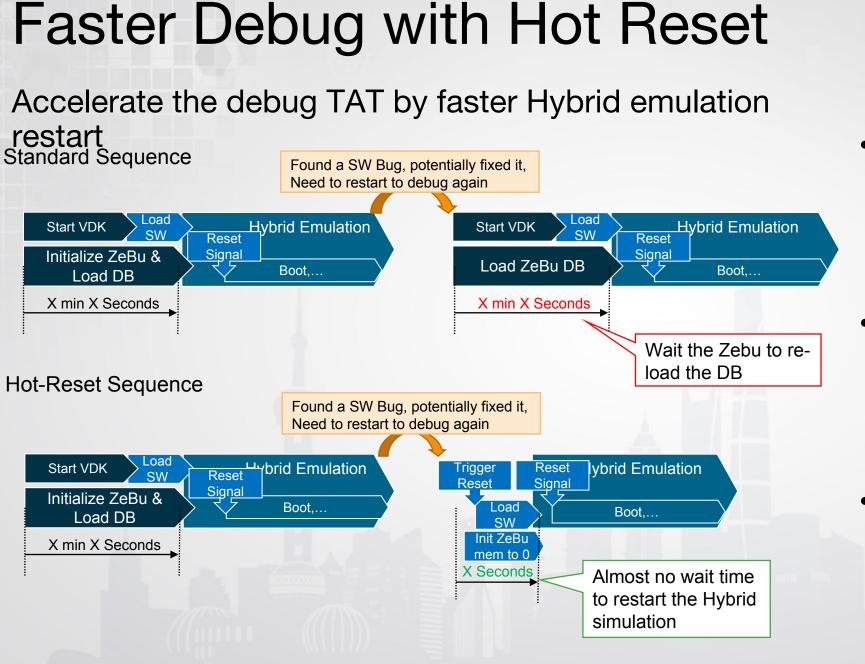

# **Higher Hybrid Debug Productivity**

### Unified ZeBu-Virtualizer views for Single-window

Forced Signals **Pinned Signals**

- **RTL** browser •

- Access to all DUT signals

- Runtime monitor

- System Clock Status

- **XTORs Readiness** Status

- Runtime control

- Waveform dump (FWC, QiWC, Dynamic Probe)

- Triggers

- **E**orooo . /

CAPTURING

CAPTURING

3 3

Value

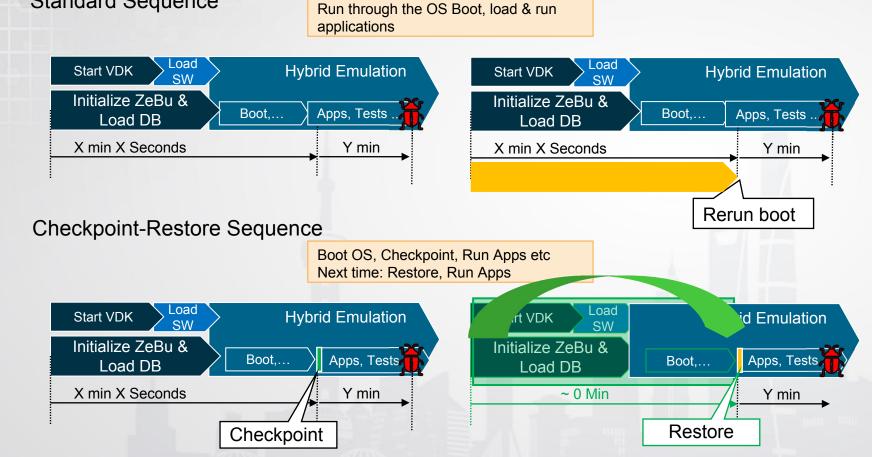

# Hybrid Checkpoint Restore

### Enables fast turn around time for boot & run,

### debugging Standard Sequence

- Bypass boot sequence for consecutive tests

- Save Hybrid Setup

- HW DUT in ZeBu

- Virtualizer Platform including files and configurations

Restore Hybrid State

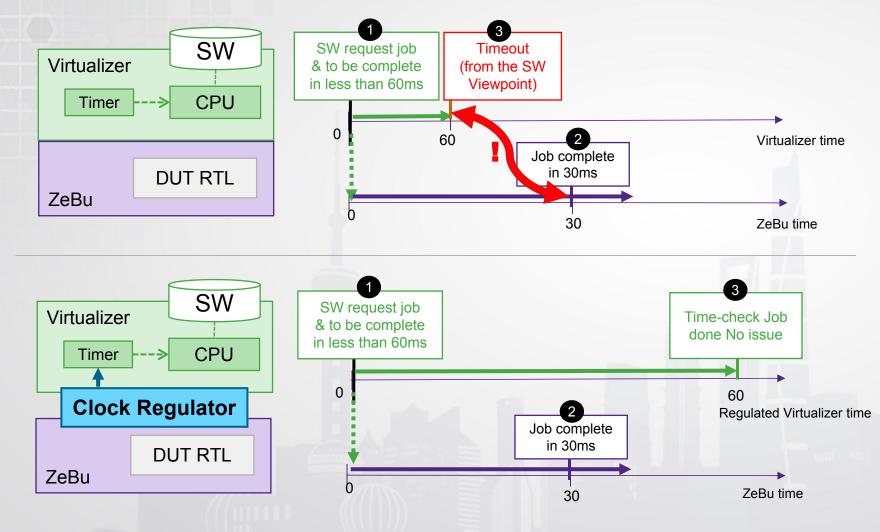

# Hybrid Clock Regulator

### Time alignment between Software and Hardware

- Purpose

- Resolve timeout issues between Fast (Software) and Slow (DUT in Hardware) side Hybrid components

- Maintain speed

- Technology

- Clock regulator to align timer in Virtualizer with execution in ZeBu

- No need to "hack" Software

- No trial and error to figure out timer & ZeBu clock settings

Reduce the restart time to only a few seconds

No Design Database reload

Load and test multiple SW Images at Runtime

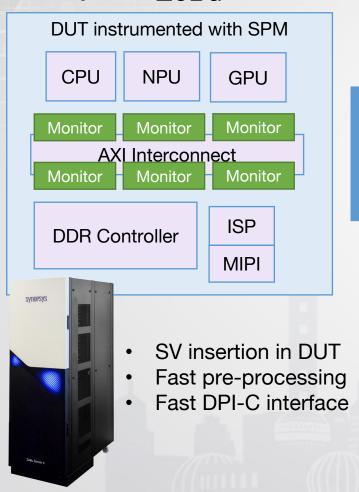

# Validate Performance at High Spectrum Conference and High Spectrum Conference and High Spectrum Conference and Exhibiting Conference and Exhibiting

### Smart Monitors for Performance and Transactional Analysis <sub>ZeBu</sub> Platform Architect

- Automatic launch & configuration

- Fast & efficient analysis database

- Stream performance analysis

- Batch / Post-run

- Dynamic / On-line

### Performance monitoring at SoC Interconnects

SHANGHAI | MAY 26, 2021

accel

SYSTEMS INITIATIVE

- Throughput, Latencies Command/Data/ Transactions

- Assertion-based max command latency violation checks

- Transactional Monitoring for Memories and Bus Interfaces

- < 5% emulation speed impact

# Conclusion

- Software and System Validation drives more than 50% of design cost and timelines

- Early HW/SW system verification is key for time to market

- Synopsys Hybrid is widely adopted in the industry to address early HW/SW system verification

- Synopsys has the largest investment in virtual prototyping, emulation and continues to innovate in new hybrid technologies

# Thank You

Q & A