# Checking Solution for the Modern Soc Design

Wanggen Shi, Big Fish Semiconductor Ltd., China Yuxin You, Mentor, a Siemens Business, China Kurt Takara, Mentor, a Siemens Business, USA

## **BigFish Overview**

- Focus on AI & IoT and chip solution

- Capability including SoC, sw Dev.& OS, Modem tech, Software&Hardware system integration and Design of 2C&2B products

- Products including mobile, UAV, super Ethernet ,IoT...

## The Need for RDC Verification

- Why reset issues are a problem?

- Asynchronous reset domain crossing cause metastability

- Reset issues result in unreliable functionality or possible silicon damage

- Functional simulation detection is probabilistic

- Reset domain crossing (RDC) verification

- Static and formal methods detect RDC issues in RTL designs

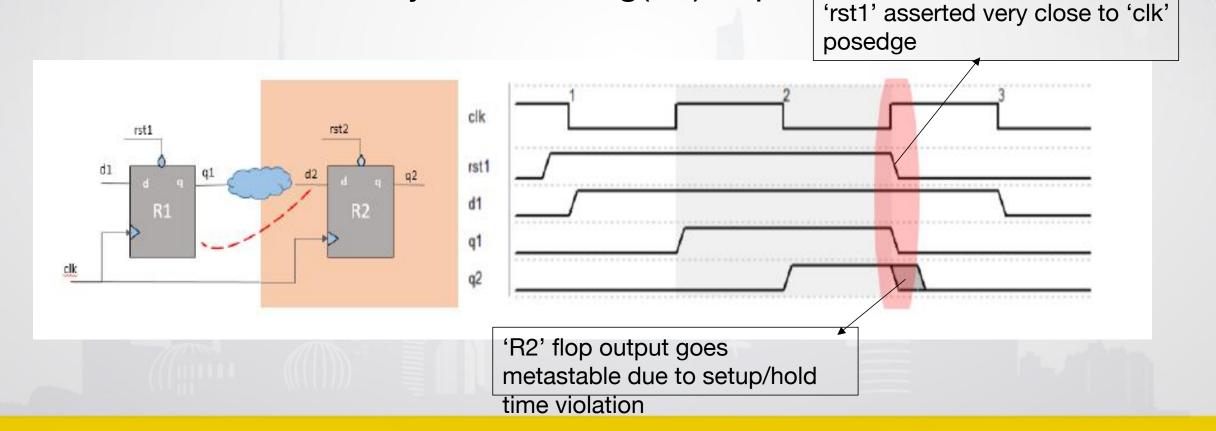

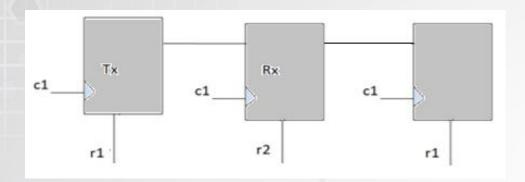

## What is RDC?

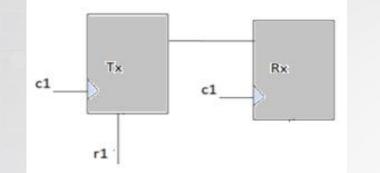

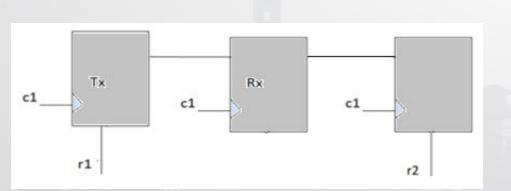

- Data crossing from one async reset domain to another

- Transmitting(Tx) flop async-reset assertion close to clock edge can cause metastability on receiving(Rx) flop

## Techniques to Address RDC issue

SHANGHALL MAY 26. 202

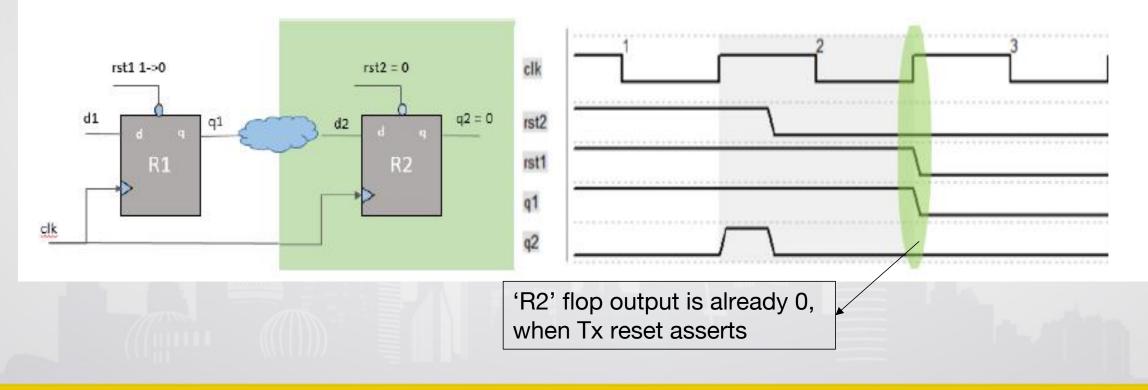

#### Reset Sequencing

- Async-reset on Rx flop always asserts before async-reset on Tx flop

- Rx flop already in reset state, so any change on Rx D-pin will not cause metastability

# Techniques to Address RDC issue

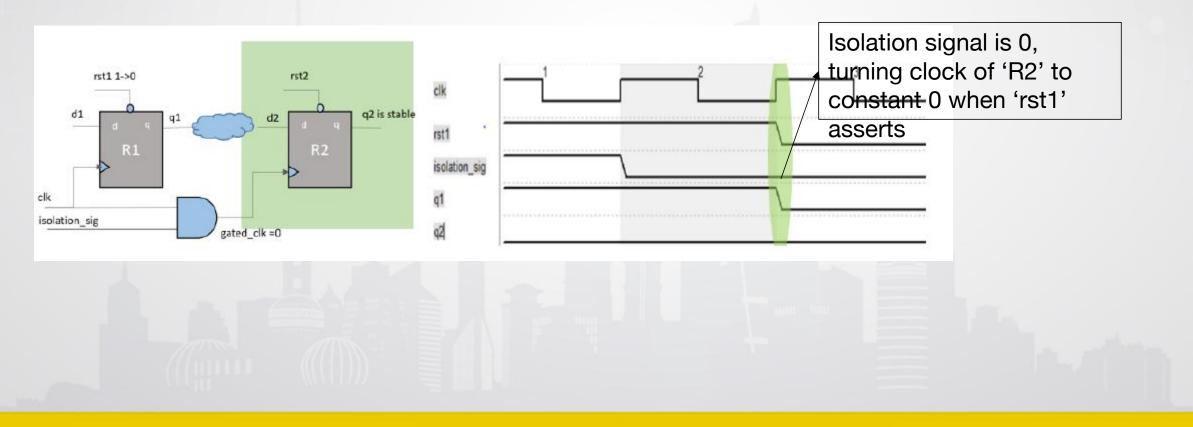

#### Clockgate isolation

- Turn off clock of Rx flop before Tx reset asserts

- If clock is off, then any change on Rx D-pin will not cause metastability

## Techniques to Address RDC issues

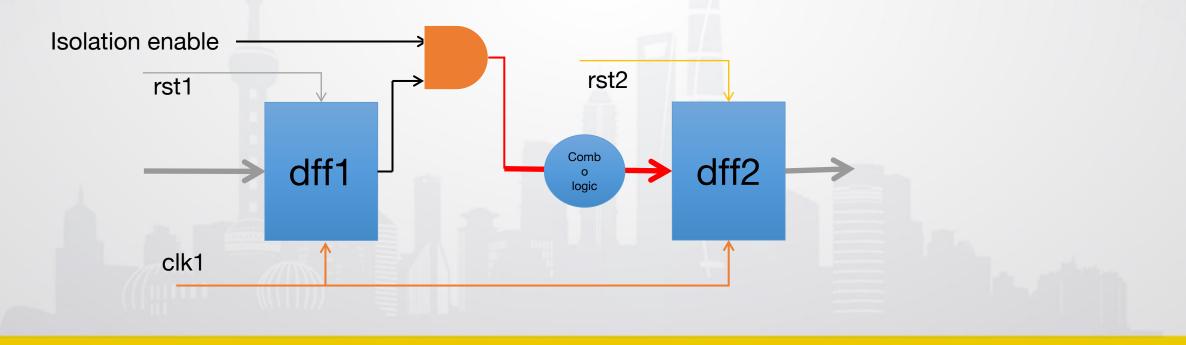

- Data Isolation

- Isolation signal from a reset controller isolates the output of the first flop when its reset is asserted. There is a handshake protocol between the enables and the corresponding resets.

- There is a mapping between isolation enables and resets

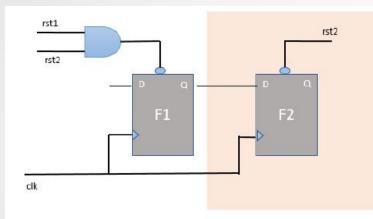

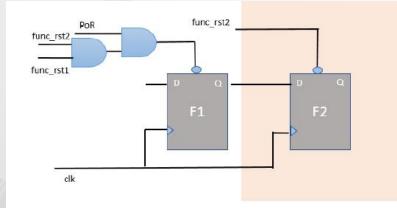

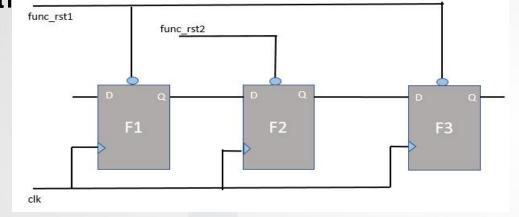

#### Combination of resets on Tx or Rx flop

If rst1 asserts before rst2, metastability can occur on F2

8

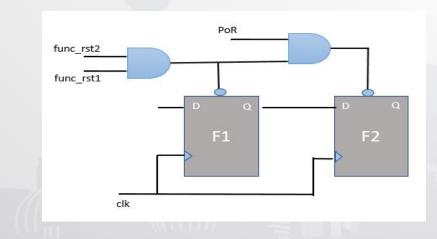

If func\_rst1 or PoR asserts before func\_rst2, metastability can occur on F2

Glitch in gated clock output due to different asynchronous reset

## Safe-RDCs Examples

Some scenarios which may look to be RDC issue, but actually safe nather

Fanouts of Rx Flop(F2) transmits to Tx Reset Domain (func\_rst1) Tx reset assertion blocks metastability

transmission

When Tx reset is asserted (through func\_rst1/func\_rst2) it always asserts Rx reset

## **RDC at Reset-less Register Example**

Unsafe crossing: From an async reset domain flop to a resetless flop

RDC Safe fanout: From an async reset domain flop to resetless flop followed by same async reset domain flop

Unsafe crossing: From an async reset domain flop to a resetless flop followed by different async reset domain flop

## Safe RDC Fanout Example

Meta-stability introduced at Rx flop is suppressed at next flop with Tx reset domain.

Safe crossing: From an async reset domain flop to another async reset domain flop followed by same Tx reset domain flop.

Back to back 2DFF structure at Rx, synchronizes the RDC.

Synchronized crossing: From an async reset domain flop to back to back two resetless flops forming a 2dff synchronizer.

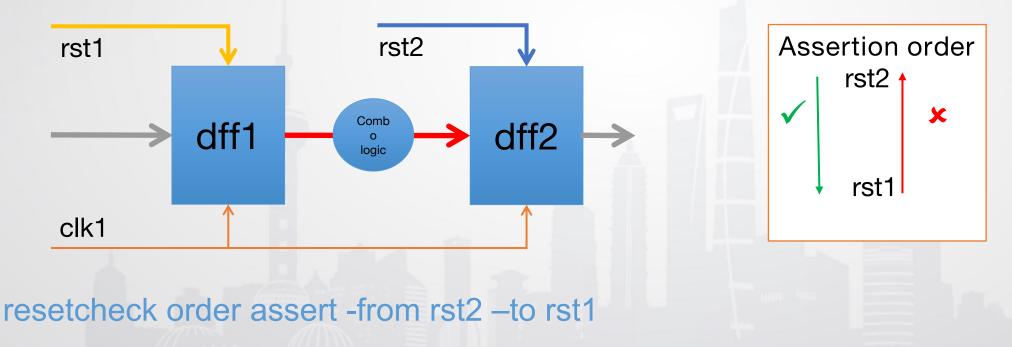

#### **Reset assertion Ordering**

Meta-stability occurs only if Rx flop is in functional mode, while Tx reset occurs. If assertion of rst2 is guaranteed to occur before rst1, it's safe RDC. If assertion of rst1 can occur before assertion of rst2, it's an RDC issue.

#### 2021 DESIGN AND VERIFICATION **Recommended RDC Verification** accellera CONFERENCE AND EXHIBITION CHINA Methodology SYSTEMS INITIATIVE SHANGHAI | MAY 26, 2021 Run Static Checks Ν Clean? Constraints Verify Constraints Run Formal Analysis Ν Ν Clean? Clean? RDC

## **RDC** Verification Preparation

#### Static reset checks

- Validate reset tree integrity and RDC verification readiness

- Assist in developing constraints

- Quality constraints

- Defines reset sequencing and safe isolation enables

- Isolation enables validated by functional checks

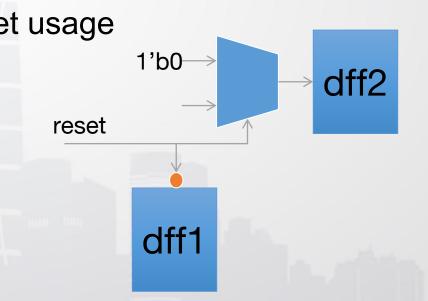

#### **Reset Tree Integrity Analysis**

Detect reset tree glitch issues

Detect inconsistent reset polarity

Detect inconsistent asynchronous/synchronous reset usage

More than 20 reset tree checks

dff2

reset

2021

dff1

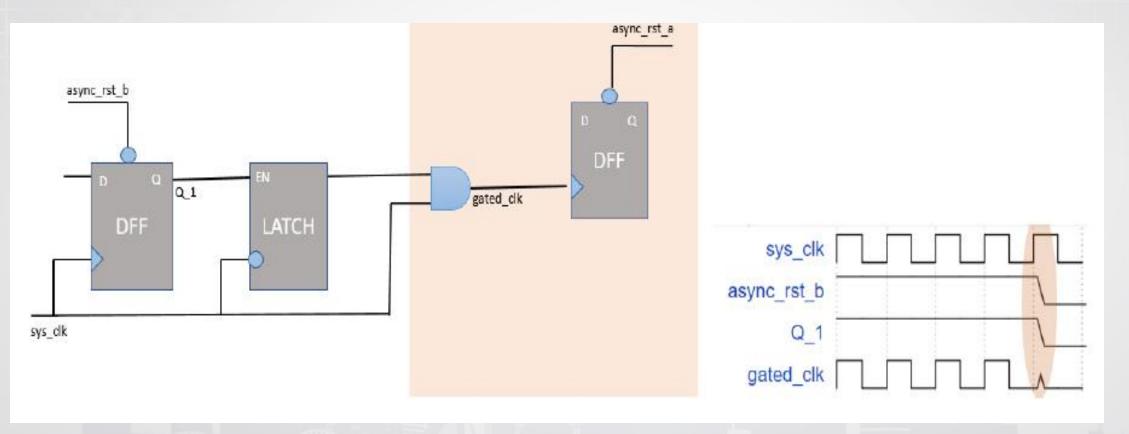

## Case Study of Project Usage

- Glitches found by static checks

- Static reset check identified potential reset glitch

- Reset glitch would occur for specific state of state machine

- Identified asynchronous FIFO issue

- Asynchronous FIFO used in a synchronous application

- TX and RX resets on asynchronous resets

- RDC verification identified a violation due to missing constraint

## **Reset Glitch Detection Case**

| Questa Verify (Output_Results/resetcheck.db)                                                                                            | ×          |

|-----------------------------------------------------------------------------------------------------------------------------------------|------------|

| <u>F</u> ile <u>V</u> iew <u>C</u> ompile Verify <u>T</u> ools <u>R</u> eports <u>L</u> ogs Layo <u>u</u> t <u>W</u> indow <u>H</u> elp |            |

| 🖹 - 🖆 🖓 🎒   🗴 🐚 鶅 ሷ 😂   🛤 🖺 😘    ResetCheck - 🐇 🕍 颷 🦉 👫 🖧 🐘   🍳 🍳 🗳 📩 🛝                                                                 |            |

| h /zin/testcases2/ktakara/fishsemi/test_reset_glitch/fsm_combo_rst.v - Default 👘 📰 📰 🛨 🖬 🗷 💽 reset_combo_glitch_1454232 - Default 🕬 👘   | + 🗗 🗙      |

| Ln# 🔄 🕸 🖗 🖗 🖗 🧏 🗲 🗲 fsm combo rst 💿 🖓 🛞 🔆 🐇 🐘 🚱 🍕 🖉 🖉 🖓 🖓 🕷 🛛                                                                           | 100×       |

|                                                                                                                                         | eset 🍘 📮   |

| <pre>32 32 assign work_flag_rstn = test_mode ? rstn : rstn &amp;&amp; !(c_st==PD); 33 34 35 35 35 35 35 35 35 35 35 35 35 35 35</pre>   |            |

| 35 always @(posedge clk or negedge work iiag rstn) begin//{                                                                             |            |

| 36 if(!work flag rstn) begin//(                                                                                                         | <u>_r</u>  |

| 37 work flag <= 0;                                                                                                                      | Q          |

| 38 active_r <= 0;                                                                                                                       | 5          |

| 39 end //)                                                                                                                              |            |

| 40 else begin//[                                                                                                                        | <u> </u>   |

| <pre>41 active r &lt;= {active r[0], active};</pre>                                                                                     |            |

| 42 if (work en)                                                                                                                         |            |

| 43 work flag <= 1;                                                                                                                      |            |

| 44 end //]                                                                                                                              |            |

| 45 end //always 0}                                                                                                                      |            |

| 46                                                                                                                                      | M          |

|                                                                                                                                         | >          |

| 🖌 Reset Static Checks                                                                                                                   | + 🗗 🗙      |

| Clear                                                                                                                                   | ar Filters |

| Severity         Status         Check         Reset         Rst Usage1         Rst Usage2         Reg Usage2                            |            |

| C Caution 2 Uninspected Potential Glitch In Reset Pa work_flag_rstn async/reset/low active_r                                            |            |

|                                                                                                                                         |            |

|                                                                                                                                         |            |

|                                                                                                                                         |            |

| 🛱 Transcript 🗶 🛞 Clocks 🗙 🛃 Resets 🗙 🌠 Reset Static Checks 🗙 🌠 Reset Checks 🗙                                                           | < >        |

## **FIFO RDC Detection Case**

2021 DESIGN AND VERIFICATION CONFERENCE AND EXHIBITION CONFERENCE AND CONFERENCE AN

| <u>V</u> iew <u>C</u> ompile Verify <u>T</u> o | ols <u>R</u> eports <u>L</u> ogs Layo <u>u</u> t <u>W</u> | indow <u>H</u> elp                     |                                               |                                      |                    |                  |                      |          |                      |             |

|------------------------------------------------|-----------------------------------------------------------|----------------------------------------|-----------------------------------------------|--------------------------------------|--------------------|------------------|----------------------|----------|----------------------|-------------|

| - 🚘 🔲 🤹 🚑 I 🐰 🕅                                |                                                           | ResetCheck — 🍈 🕍 🌉 🐉 🚛                 | Layout Last Se                                | ttings 🔻 🔍 🔍 🔍                       |                    |                  |                      |          |                      |             |

| esign                                          |                                                           | + @ ×                                  | rdc areset 6255538                            |                                      |                    |                  |                      |          |                      | +           |

| Instance                                       | Design Unit                                               | Design Unit Type                       |                                               | ्र 🔶 🛷 🦗 । 🔍 🔍 🔍 🔳                   | 🖏 🗔 🔉 🗙 ហ 🖞        | ×   ]& ->[ ], ]; |                      |          |                      |             |

| demo top (3)                                   | demo top                                                  | Top Module                             |                                               |                                      |                    |                  | 1 d                  |          |                      | Reset       |

| T dello_op (3)                                 | demo_top                                                  | Top module                             |                                               |                                      |                    | 1110             | 10 10 10 10 10 10    |          |                      | Neber       |

|                                                |                                                           |                                        |                                               |                                      |                    |                  | almost_empty_d       |          |                      |             |

|                                                |                                                           |                                        |                                               |                                      |                    |                  | almost_empty_s       |          |                      |             |

|                                                |                                                           |                                        |                                               |                                      |                    |                  | almost_full_d        |          |                      |             |

|                                                |                                                           |                                        |                                               |                                      |                    | ae_level_d       | almost_full_s        |          |                      |             |

|                                                |                                                           |                                        |                                               |                                      |                    | ae level s       | clr_cmplt_d          |          |                      |             |

|                                                |                                                           |                                        |                                               |                                      |                    | af level d       |                      |          |                      |             |

|                                                |                                                           |                                        |                                               |                                      |                    |                  | <u>clr_cmplt_s</u>   |          |                      |             |

|                                                |                                                           |                                        |                                               |                                      |                    | af_level_s       | clr_in_prog_d        |          |                      |             |

|                                                |                                                           |                                        |                                               |                                      |                    | clk_d            | <u>clr_in_prog_s</u> |          |                      |             |

|                                                |                                                           |                                        |                                               |                                      |                    | clk_s            | clr_sync_d           |          |                      |             |

|                                                |                                                           |                                        |                                               |                                      | 1.451.51           | clr d            | clr_sync_s           |          |                      |             |

|                                                |                                                           |                                        |                                               |                                      | data               | clr s            | data_d               |          |                      |             |

|                                                |                                                           |                                        |                                               |                                      |                    | × – –            |                      |          |                      |             |

|                                                |                                                           |                                        |                                               |                                      |                    | data_s           | empty_d              |          |                      |             |

|                                                |                                                           |                                        |                                               |                                      | tat tat            | init_d <u>_n</u> | empty_s              |          |                      |             |

|                                                |                                                           |                                        |                                               |                                      |                    | init_s <u>_n</u> | error_d              |          |                      |             |

|                                                |                                                           |                                        |                                               |                                      |                    | pop_d <u>_n</u>  | error_s              |          |                      |             |

|                                                |                                                           |                                        |                                               |                                      |                    | push_s_n         | fifo_empty_s         |          |                      |             |

|                                                |                                                           |                                        |                                               |                                      |                    |                  |                      |          |                      |             |

|                                                |                                                           |                                        |                                               |                                      |                    | rst_d_n          | fifo_word_cnt_s      |          |                      |             |

| Project 🗶 📶 Library 🗶 🖼 [                      | Directives 📰 💷 Design 🛪 🍱 M                               | lodules 🛛 🌠 Reset Policy Checks 🗶 🍕    |                                               |                                      |                    | rst_s_n          | full_d               |          |                      |             |

|                                                |                                                           |                                        |                                               |                                      |                    | N                |                      |          |                      |             |

| Reset Checks                                   |                                                           |                                        |                                               |                                      |                    |                  |                      |          |                      | : •         |

| 🖾 Waived 🔽 🖬 Fixed 🔽                           | Pending 🔽 Uninspected                                     | 🔽 🖪 Bug 🗌 💟 Verified 🛛 🛷 Apply         | Select                                        |                                      |                    |                  |                      |          |                      | Clear Fi    |

| Severity Statu                                 | s                                                         | Check                                  |                                               | Tx Signal                            | Rx Signal          | Tx Reset         | △ Tx Reset Type      | Rx Reset | Rx Reset Type        | Tx Clock    |

| 🗄 🏧 Violation 😢                                | Uninspected                                               | Reset Cdc Has No Synchronizer (6       | 9)                                            | 1                                    | 1                  |                  |                      |          |                      | 1           |

| Violation 2                                    | Uninspected                                               | Reset Domain Crossing From Ares        |                                               |                                      |                    |                  |                      |          |                      |             |

| Viola 2                                        | Uninspected                                               | Reset Domain Crossing From Ares        | et To Areset                                  | fifo_1_d. <protected>.in</protected> | nu pass_valid      | clr              | user/async/reset/low | rst      | user/async/reset/low | mac_clk_in  |

| Viola 2                                        | Uninspected                                               | Reset Domain Crossing From Ares        | et To Areset                                  | header                               | tx_wcnt            | cir              | user/async/reset/low | rst      | user/async/reset/low | core_clk_in |

| Viola 2                                        | Uninspected                                               | Reset Domain Crossing From Ares        |                                               | data                                 | tx_mask            | clr              | user/async/reset/low | rst      | user/async/reset/low | core_clk_in |

| Viola 2                                        | Uninspected                                               |                                        | eset Domain Crossing From Areset To Areset    |                                      | lat crc_1.scramble | clr              | user/async/reset/low | rst      | user/async/reset/low | mac_clk_in  |

| Viola 2                                        | Uninspected                                               |                                        | Reset Domain Crossing From Areset To Areset   |                                      | fifo_1_dzicne      |                  | user/async/reset/low | rst      | user/async/reset/low | core_clk_in |

| Viola 2                                        | Uninspected                                               | Reset Domain Crossing From Ares        |                                               | mask                                 | rx_masked_data[0]  | rst              | user/async/reset/low | clr      | user/async/reset/low | mac_clk_in  |

| Violation 2                                    | Uninspected                                               | Combinational Logic Before Rdc S       | (2)                                           |                                      |                    |                  |                      |          |                      |             |

| ]                                              |                                                           |                                        |                                               |                                      |                    |                  |                      |          |                      |             |

| Transcript 🗙 🕒 Clocks 🗙 🛓                      | 🛾 Resets 🛛 🌠 Reset Setup Che                              | ecks 🕺 🎻 Reset Static Checks 🗶 🌠 Reset | Checks ×                                      |                                      |                    |                  |                      |          |                      |             |

| ters in use: 0                                 | <no context=""></no>                                      |                                        | 1978 - C. |                                      |                    |                  |                      |          |                      |             |

## **Future Plans**

- Utilize constraints and waivers to achieve RDC verification closure

- Verify constraints with SVA assertion flow

- Verify low-power structures with PA-RDC

- For larger designs, utilize hierarchical RDC flow

## Summary

- Increase in SoC reset architecture complexity requires RDC verification

- RDC verification methodology provides completeness and efficiency

- RDC verification metrics demonstrate verification completion

- Achieved our goal of reliable silicon operation!

## Thanks you