#### Introduction

- Overview of the main contents: What does this paper talk about?

- Overview of background : Why do this work?

- Unified Verification Management Tool

- Basic steps for manage verification process

- The basic functions of the tool

- Reusable testcase build method

- How to implement this method

- Show some sample code

## The Main Contents of This Paper

This paper introduces a verification management tool that unifies the process construction of front-end verification, prototype verification and post-silicon validation in order to free verification engineers from the complicated process development and enable them to focus on the chip function itself so as to better complete the most important work. It realizes the functions of test case management and automatic execution of test cases.

# The Main Contents of This Paper

Present a method of reusing test cases between front-end verification, prototype verification and post-silicon. The use of test case reuse method can significantly improve the efficiency of use case management in different verification stages and reduce the workload of test case development on the basis of the verification management tools described in this paper.

- SoC technology has made great progress with the progress of semiconductor manufacturing technology. The size and complexity of chips have increased exponentially.

- The current verification of SoC chips is facing more difficulties and challenges, and the verification technology of SoC chips based on FPGA is one of the important ways to solve this problem.

- FPGA can accelerate verification and truly simulate the working state of the actual SoC chip, so it can make up for the defects in the simulation phase, thus greatly improving the success rate of taping.

- The prototype verification and post-silicon verification of the chip design process can effectively ensure the quality of the chip.

- Improving the work efficiency and automation of these two stages can free verification engineers from the complicated process development and enable them to focus on the chip function itself so as to better complete the most important work.

- Considering that there are basically the same requirements for test case management and regression testing process in different stages of verification, a verification management tool is developed.

- This paper focuses on the regression test automation.

- Introduces this verification management tool, which unifies the process of front-end verification, prototype verification and post-silicon validation.

- It realizes the functions of test case management and automatic execution of test cases.

- Because the prototype verification and post-silicon verification sometimes are very consistent with the front-end verification in the test scenario, a test case reuse design method is developed from the point of view of increasing the reusability of test cases.

- This paper will introduce some designs to improve reusability in the front-end verification process based on a unified method. The front-end test cases designed based on this method can be reused in the prototype verification and post-silicon verification phase. After all, it can significantly save the time of verification use case development.

- It uses a unified verification management tool to deal with different stages of verification work.

- Based on this method, the management and automatic execution of test cases can be realized.

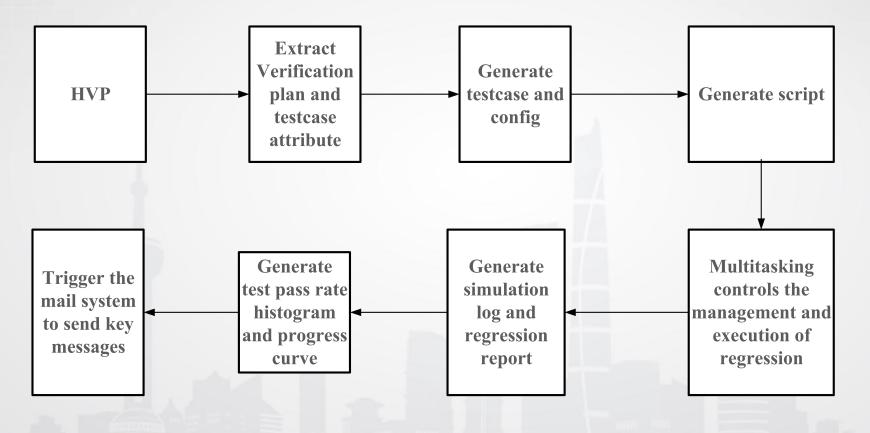

- This method divides the execution process of test cases into three stages: verification preparation, verification execution and post-verification processing, which has a high degree of expansibility.

- Personalized processes and functions can be flexibly expanded for different stages of different test cases.

- The detail include:

- Define the attribute information of each test case

- Automatically generating the template and the configuration file of the test case according to these attribute information.

- Build a visual operating environment, and uniformly managing the test cases of multiple modules.

- Complete automatic regression testing, analyze the result log, and generate verification report.

a. Figure 1. Testcase regression system flow

#### •Define the basic configuration information of the tool

It is necessary to define some path information in advance to execute and store files when using the tool. Its form is shown in the pseudo code below. For example, GL\_SRC\_DIR represents the source file location of the test case. The details are as follows:

GL\_SRC\_DIR = \$WORKAREAD/verify\_repo/soc GL\_HVP\_DIR = \$WORKAREAD/verify\_repo/etc/vplan GL\_SIM\_DIR = \$WORKAREAD/playground/toolrun/simulation/soc

#### Definite HVP

HVP, as the only input source, contains the necessary attributes of the test case definition. The detail is as follows:

```

plan CPU_VPLAN;

attribute string owner = "Zhang San";

attribute string module_name = "cpu";

feature VO_CPU_IRAM_TEST;

description = "test mem size"

measure test_status, test_status.percent.PASSED test_status;

source = "cpu_iram_size_test"

endmeasure

endfeature

```

#### Extract test cases and add corresponding methods

- They automatically extract the information from the HVP and build a data structure for all the test cases it contains, in order to save the properties of each test case and display it in the tool window when users select the specified HVP through the tool interface.

- In the meanwhile, a variety of methods are provided for each test case, including test case file generation, use case execution, log viewing, and so on.

- Generate test case simulation configuration file

- The simulation is divided into three stages:

- pre-processing

- Running

- post-processing.

pre\_cfg: target\_name:

- target\_name: example\_target\_name

- pre\_cmd\_list:

- pre\_cmd\_list:

- example\_pre\_cmd1

- \$(sim\_dir)/example\_pre\_cmd2

run\_cfg:

run\_opts:

- run\_opts: "example\_opt1 example\_opt2"

post\_cfg:

post\_cmd\_list:

- post\_cmd\_list:

- \$(sim\_dir)/example\_post\_cmd1

- example\_post\_cmd

#### Generate Shell script

• Each test case generates a corresponding Shell file.

echo "pre-processing" module load python/3.7.5 cp -fr /home/cadadm/scripts/\* /nfs/simulation/example In -sf /home/cadadm/etc/\*.sh /nfs/simulation/example echo "runing" python ./run\_test.py echo "post-processing perl ./check\_result.pl

#### Regression management

- When multiple test cases are submitted, the number of tasks to be run can be limited according to the maximum number of tasks set.

- The status of each test case can be monitored in real time. Once a task is completed, the remaining tasks to be submitted will be executed until all regression test cases are completed.

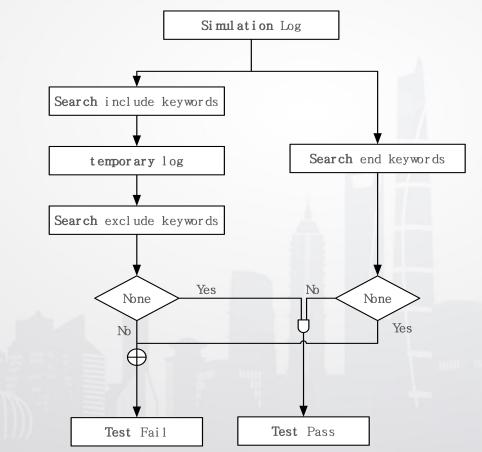

Check the simulation log to determine the result

#### Generate reports

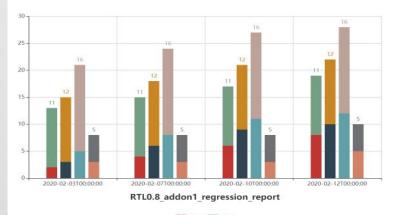

- Users can generate the results of all test cases through the UI, including the HVP, maintainer, run time, results and other information.

- According to the log information, users can draw the bar chart, pie chart to show the proportion of different priorities, and the test pass ratio of different modules, and compare the results of each regression curve.

# • WHAT & WHY

- This paper intends give a method to improve the reusability of test cases in view of the consistency of verification scenarios in the three stages of front-end verification, prototype verification and post-silicon validation.

- This method can complete most of the development of prototype verification test cases during the front-end verification, and the test cases developed at this stage will be reused in the post-silicon verification phase.

- This method can significantly reduce the workload of test case development in prototype verification and post-silicon validation phase.

### • HOW

- We need to find something in common among the verification environments of front-end verification, prototype verification and post-silicon verification by considering the reusability of test cases.

- Prototype & post\_silicon validation:

- Send the test incentive to the DUT through the real interface.

- Load FW from external storage and executes it.

- Front-end verification:

- Simulate the incentive process, such as issuing various types of control/data plane configuration according to the software flow.

## • HOW

- In this process, the incentive content of front-end verification is highly consistent with prototype verification and post-silicon verification.

- We can unify the implementation methods of different verification stages in this process, to achieve the reuse of test cases in different verification stages.

- There are many ways to realize this stimulation process. C language is used to write test incentives in front-end verification from the point of view of maintainability and expansibility.

- The method of DPI provided by SystemVerilog language is adopted to combine the test incentives written in C language with the verification platform written by SystemVerilog.

- The following is a simple example to illustrate this design idea and the basic implementation method. The code example can be seen as follows.

# SYSTEMS INITIATIVE

#### SystemVerilog Code:

import "DPI-C" context task dpi\_c\_thread(); class dpi\_test extends base\_test;

. . . task dpi\_test::run\_phase(uvm\_phase) phase);

dpi\_c\_thread();

. . . endtask : run\_phase endclass

#### C Code:

void dpi\_c\_thread(){ config()

Void config(){ reg\_write(addr\_1, value\_1)

. . . reg\_write(addr\_n, value\_n)

The basic function task, method written by SystemVerilog is also called using DPI in dpi\_c\_thread as shown below.

```

export "DPI-C" reg_write = task reg_write(int addr, int value);

```

```

task reg_write (int addr, int value);

/*configuration procedure*/

```

```

endtask

```

#### Conclusion

- This paper implements a unified verification management tool. It can not only improve the work efficiency, but also reduce the repeated investment in verification management in different verification stages.

- And this paper also intends give a method to improve the reusability of test cases. It can reduce the workload of test case development for verification engineers at different verification stages.

- We will consider how to further improve the methods and tools of cooperation between different verification stages based on the view that unifying the tools and methods of different verification stages can reduce repetitive investment and improve work efficiency.

# Thanks!